Pourquoi est-ce important: Intel, propulsé par Pat Gelsinger, a connu un grand succès avec le lancement d’Alder Lake, mais la société a de grandes ambitions pour l’avenir. Selon un brevet qui a récemment fait surface en ligne, Team Blue pourrait utiliser des transistors « forksheet empilés » pour maintenir la loi de Moore en vie.

À l’heure actuelle, ce n’est un secret pour personne qu’Intel a suivi un train de transformation culturelle sous la direction de son nouveau PDG, Pat Gelsinger. Le patron de Team Blue est un leader franc et trop optimiste, ce qui a restauré une certaine confiance des investisseurs au cours de l’année écoulée. Avec le lancement réussi des premiers processeurs Alder Lake de la société, Gelsinger pense que la conquête par Ryzen du marché des ordinateurs de bureau passionnés par AMD pourrait toucher à sa fin.

Au-delà du battage médiatique, Intel a besoin de temps pour récupérer sa couronne de fabrication de puces, ce qui pourrait prendre des années. Au cours des derniers mois, la société a dévoilé plusieurs nouvelles technologies de processus et de conditionnement en cours de développement, notamment de nouveaux transistors 3D, l’intégration logique à logique Foveros et le pont d’interconnexion multi-Die intégré (EMIB).

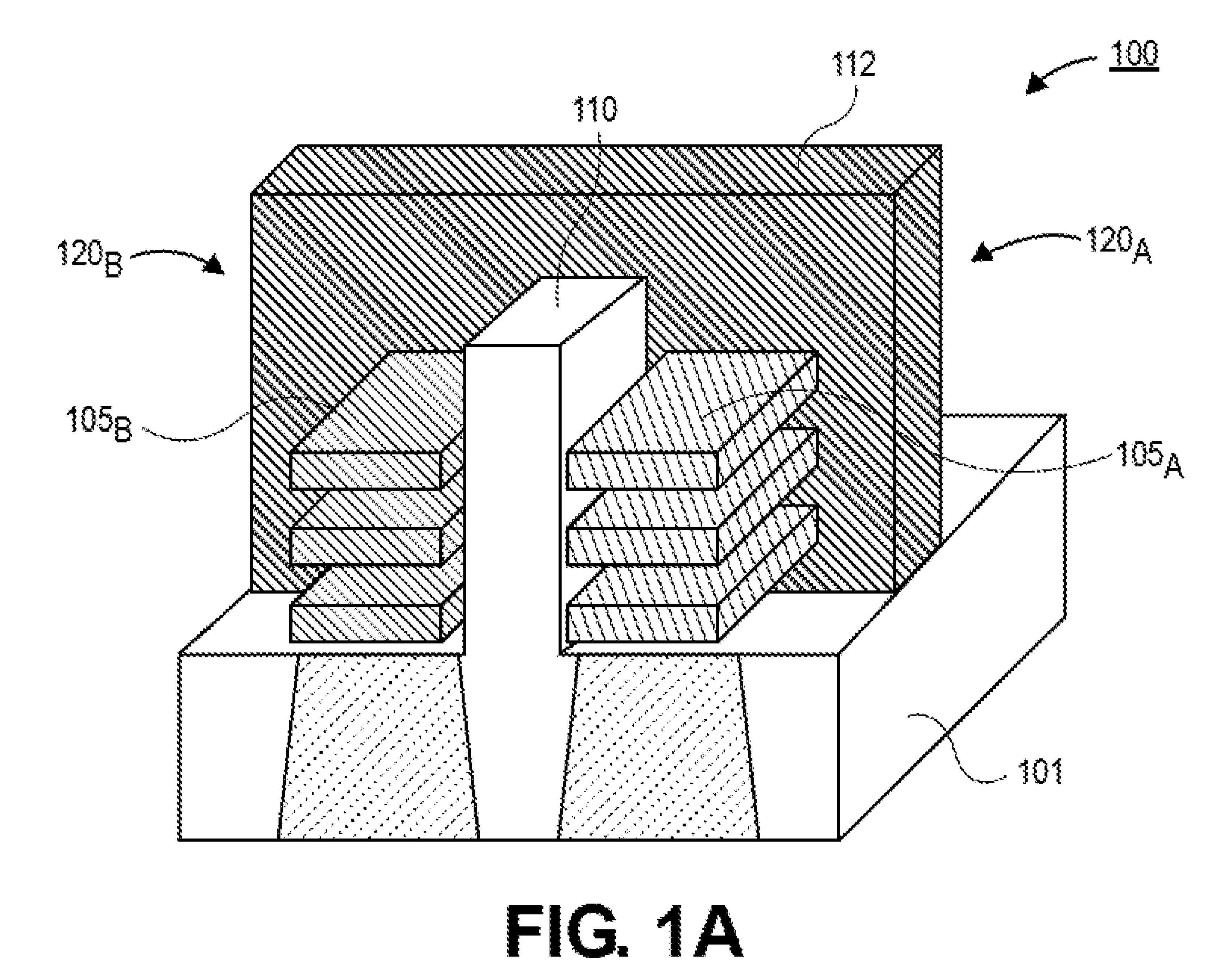

Cependant, l’aspect le plus intéressant des aspirations d’Intel à devenir un leader de processus se trouve dans ses derniers brevets. L’un d’eux décrit ce qu’Intel appelle un « transistor à feuille de fourche empilé», ce qui est essentiel pour maintenir la loi de Moore en vie aux nœuds de processus inférieurs à 3 nm.

Le brevet lui-même n’inclut aucune revendication d’amélioration de la puissance-performance-zone (PPA), mais il révèle comment Intel envisage une architecture CMOS empilée verticalement qui pourrait permettre des densités de transistors plus élevées dans les conceptions futures. Cela aurait un coût élevé en termes de complexité de fabrication, et Intel affirme que la réduction supplémentaire des transistors nécessite un compromis entre la plus petite taille d’une caractéristique modelée dans une pile de semi-conducteurs et l’espacement entre ces caractéristiques.

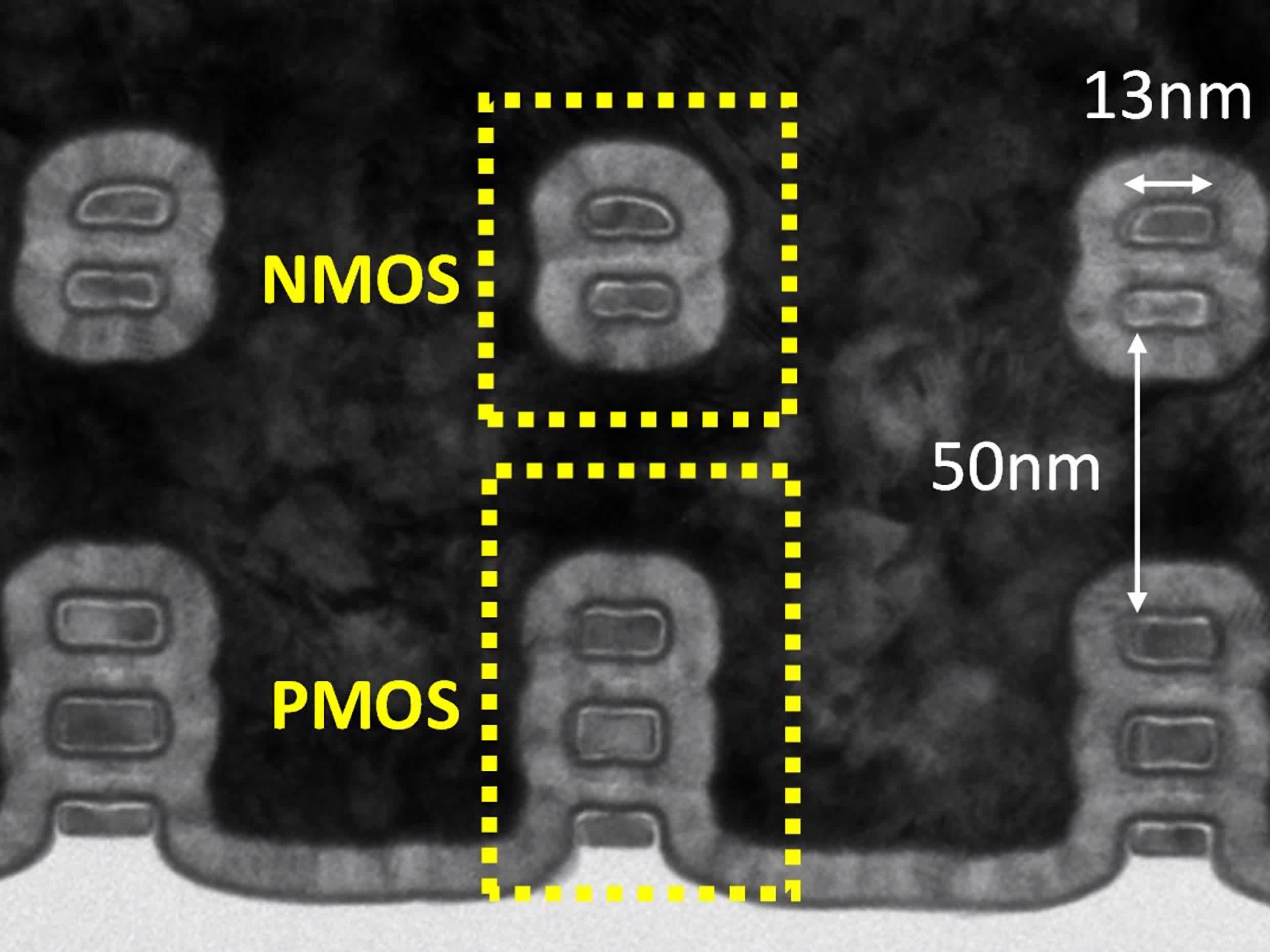

Intel explore l’idée d’utiliser des transistors « nanoribbon » qui peuvent être empilés les uns sur les autres à l’aide d’un film mince de germanium qui sert de couche de séparation diélectrique. Cela permettrait à l’entreprise de rapprocher beaucoup plus les transistors PMOS et NMOS sans affecter leur fonctionnement. À tout le moins, cela devrait conduire à réduire de moitié l’encombrement d’un simple dispositif CMOS, donc essentiellement à doubler la densité des futurs circuits intégrés.

Comme c’est noté par Tom’s Hardware, un groupe de recherche basé en Belgique appelé Imec a également exploré un concept similaire baptisé FET complémentaire (CFET) et effectué des simulations sur un nœud de processus de 2 nm. Les résultats ont montré une augmentation de 10 % de la vitesse ou une amélioration de 24 % de l’efficacité énergétique par rapport aux conceptions de nanofeuilles traditionnelles, associées à une réduction de 20 % de la surface cellulaire. De plus, cela pourrait réduire l’empreinte du cache d’un processeur – qui occupe généralement une énorme partie de la zone de matrice – de 30% encore plus impressionnant.

Cette recherche a été menée en 2019 et les composants construits par Imec n’étaient pas entièrement construits à partir de transistors nanosheet/nanoribbon. Au lieu de cela, ils étaient constitués d’une couche FinFET inférieure avec une seule nanofeuille sur le dessus, il est donc tout à fait possible que la version d’Intel puisse obtenir de meilleurs résultats.

Pour référence, TSMC affirme que son prochain nœud de processus 3 nm offrira une amélioration de 10 à 15 % des performances ou jusqu’à 30 % d’augmentation de l’efficacité énergétique par rapport à son nœud de processus 5 nm. La fonderie affirme que le nouveau nœud permet également une amélioration jusqu’à 70 % de la densité logique pour les cœurs de processeur et une amélioration de 20 % en termes de densité SRAM.

Même si la voie du brevet aux applications commerciales n’est pas encore claire, le nouveau brevet offre un aperçu de ce que fait le groupe de recherche sur les composants d’Intel pour aider les ambitions d’Intel autour des transistors gate-all-around pour des nœuds comme Intel 20A et au-delà.

En attendant, l’entreprise est occupée à étendre sa capacité de fabrication et prévoit de dépenser 25 à 28 milliards de dollars en 2022 rien que pour cela.