En un mot: TSMC vient d’annoncer le lancement de toute sa gamme de nœuds de classe 3 nm au cours des trois prochaines années. Sa nouvelle technologie FinFlex donnera aux concepteurs de puces encore plus de flexibilité pour optimiser chaque cellule standard en fonction de la consommation d’énergie, des performances et de la densité souhaitées.

TSMC vient de dévoilé toute sa famille N3 de nœuds de processus. Les concepteurs de puces tels qu’AMD, Apple, Nvidia et même Intel utiliseront ces nœuds au cours des prochaines années pour fabriquer leurs puces à la pointe de la technologie.

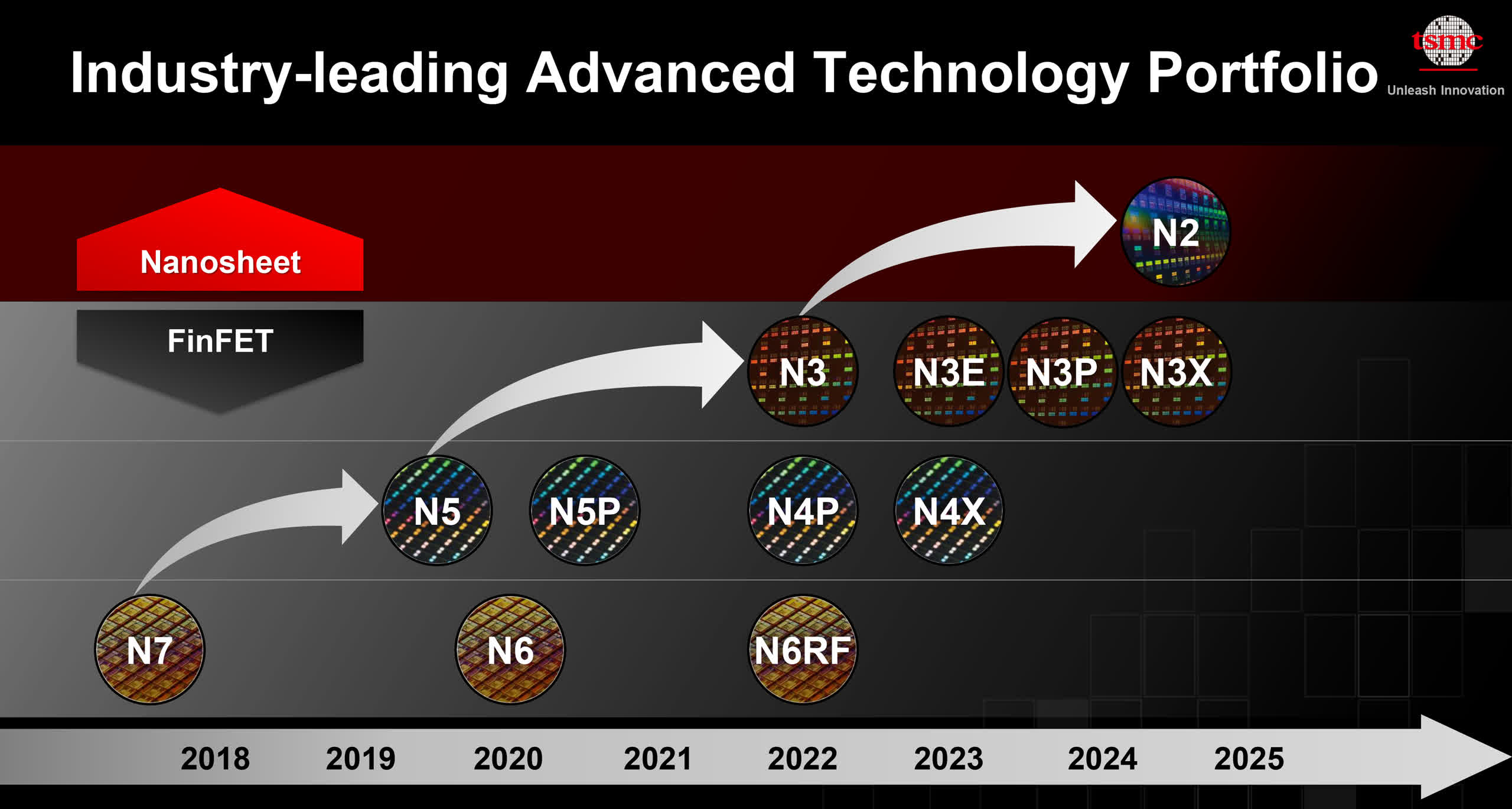

La société taïwanaise dispose d’un total de cinq nœuds de classe 3 nm différents. N3 commencera la fabrication à grand volume plus tard cette année, les premières puces devant parvenir aux clients au début de l’année prochaine. N3E sera lancé plus tard avec des améliorations de performances et d’efficacité, des rendements plus élevés, mais une densité logique légèrement réduite.

Vers 2024, TSMC sortira N3P, qui se concentre sur l’amélioration des performances. N3S, qui ne figurait pas dans la feuille de route de TSMC, n’était que brièvement mentionné en conversation avec SVP Kevin Zhang.

Enfin, N3X sortira environ un an plus tard et permettra des performances extrêmement élevées à des tensions plus élevées, l’efficacité et les coûts passant au second plan. Cette approche est similaire au procédé N4X de classe 5 nm qui commencera la fabrication en volume l’année prochaine.

Les nœuds N3 et N3E de TSMC prendront également en charge le nouveau Technologie FinFlex. Actuellement, les concepteurs de puces doivent choisir une bibliothèque pour chaque bloc dans un SoC. Avec FinFlex, ils n’auront pas cette limitation et pourront mélanger et assortir différentes bibliothèques dans chaque bloc.

Ils peuvent utiliser des FinFET 2-1 (double-gate single-fin) dans certaines parties afin de réduire la consommation d’énergie et la taille de la matrice (coût) et opter pour des FinFET 3-2 dans d’autres domaines où les performances maximales sont primordiales. Pendant ce temps, 2-2 FinFET offrent un équilibre entre taille, performances et consommation d’énergie.

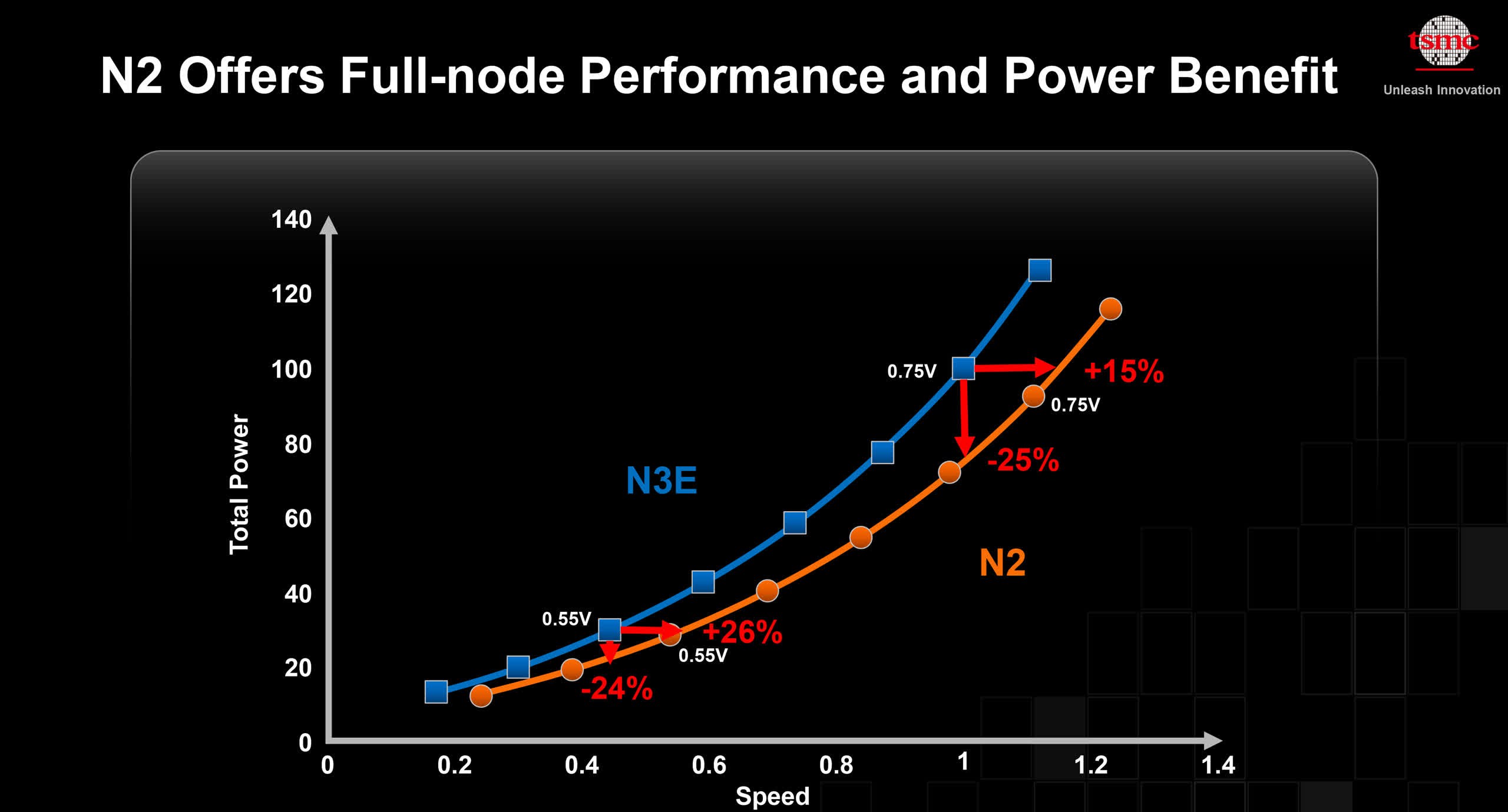

TSMC a également mentionné son prochain nœud de processus N2, qui utilisera des transistors à effet de champ tout autour de la porte (GAAFET), avec des plans pour commencer la fabrication en volume au second semestre 2025.

Par rapport au N3E, il consommerait 25 à 30 % d’énergie en moins à la même fréquence et permettrait 10 à 15 % de performances en plus avec la même consommation d’énergie et le même nombre de transistors. Pendant ce temps, la densité des puces augmenterait de plus de 10 %.