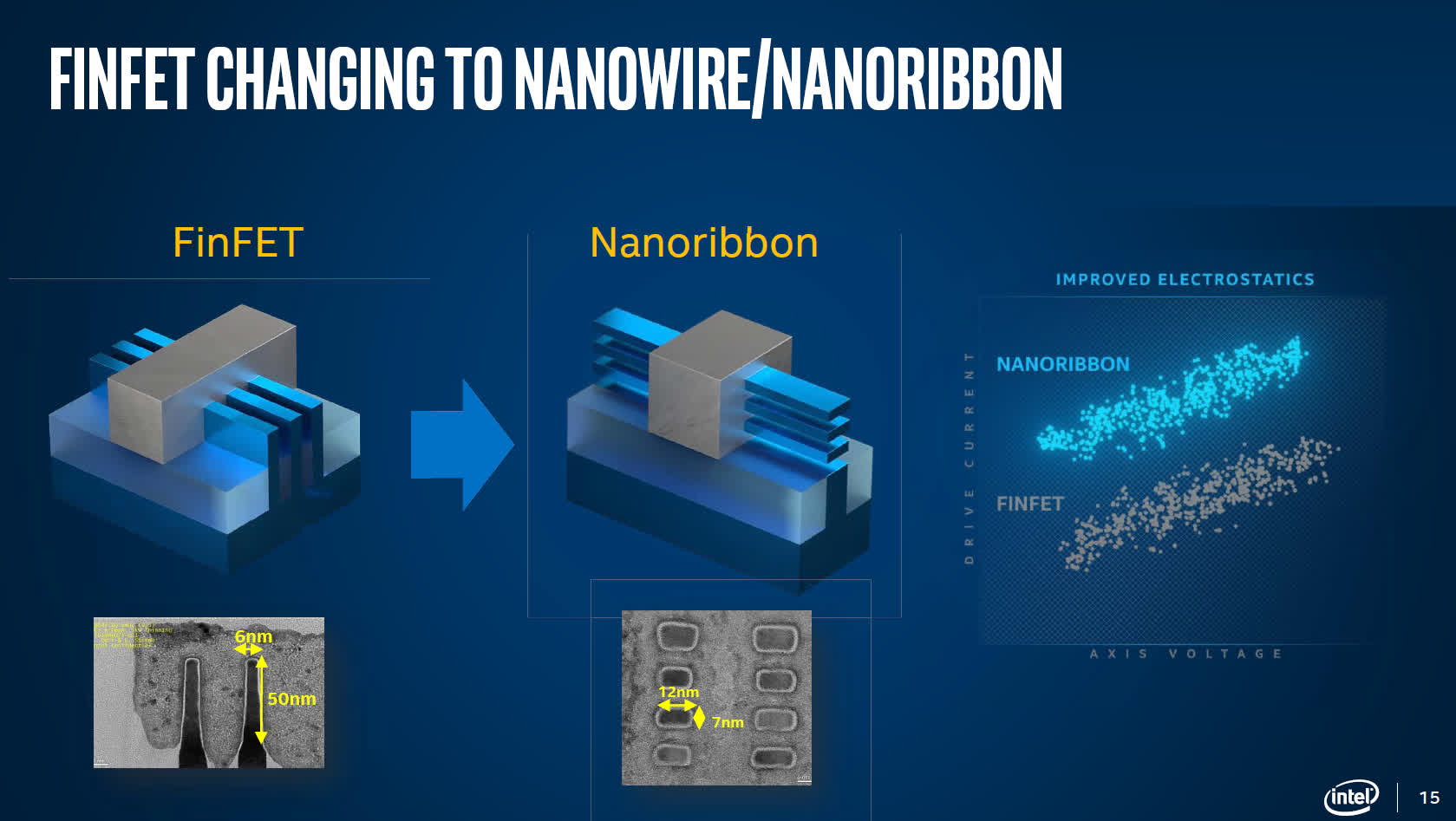

Pourquoi est-ce important: La transition des transistors planaires au FinFET a suffi à maintenir la loi de Moore pertinente pendant les 10 dernières années, mais même cette conception s’essouffle. Les transistors à porte tout autour semblent prometteurs pour 3 nm et au-delà, mais cette transition pourrait être la plus coûteuse à ce jour.

Alors que les puces les plus avancées d’aujourd’hui sont fabriquées sur un nœud de processus de 7 nm ou 5 nm, de grandes fonderies comme TSMC et GlobalFoundries ont été occupées à développer de nouveaux nœuds à 3 nm et 2 nm, basés sur des transistors à grille de nouvelle génération -FET). Bien que les GAA-FET offrent certains avantages tels qu’une meilleure évolutivité, des temps de commutation plus rapides, de meilleurs courants d’entraînement et des fuites plus faibles, FinFET reste la technologie préférée car les fabricants pensent pouvoir en tirer davantage.

Par exemple, TSMC a déclaré lors du Symposium technologique de l’année dernière que sa technologie N3 offre des performances jusqu’à 50% supérieures, jusqu’à 30% de réduction de la consommation d’énergie et, plus important encore, permet 1,7 fois la densité de N5. L’utilisation d’un nœud de processus éprouvé et plus prévisible donnera à TSMC suffisamment de temps pour tester le GAA-FET pour une utilisation à 2 nm. La dernière fois que nous en avons entendu parler, la société prévoyait d’avoir un nœud de processus 2 nm prêt pour la production de masse d’ici 2024.

Selon un rapport d’ingénierie des semi-conducteurs, Intel et Samsung travaillent également dur sur transition aux nœuds de 3 nm et 2 nm, et ce dernier pourrait le faire d’ici la fin de l’année prochaine. Il existe plusieurs types de GAA-FET, et nous savons que Samsung est Planification pour utiliser des MBC-FET à base de nano-feuilles (Multi-Bridge Channel FET).

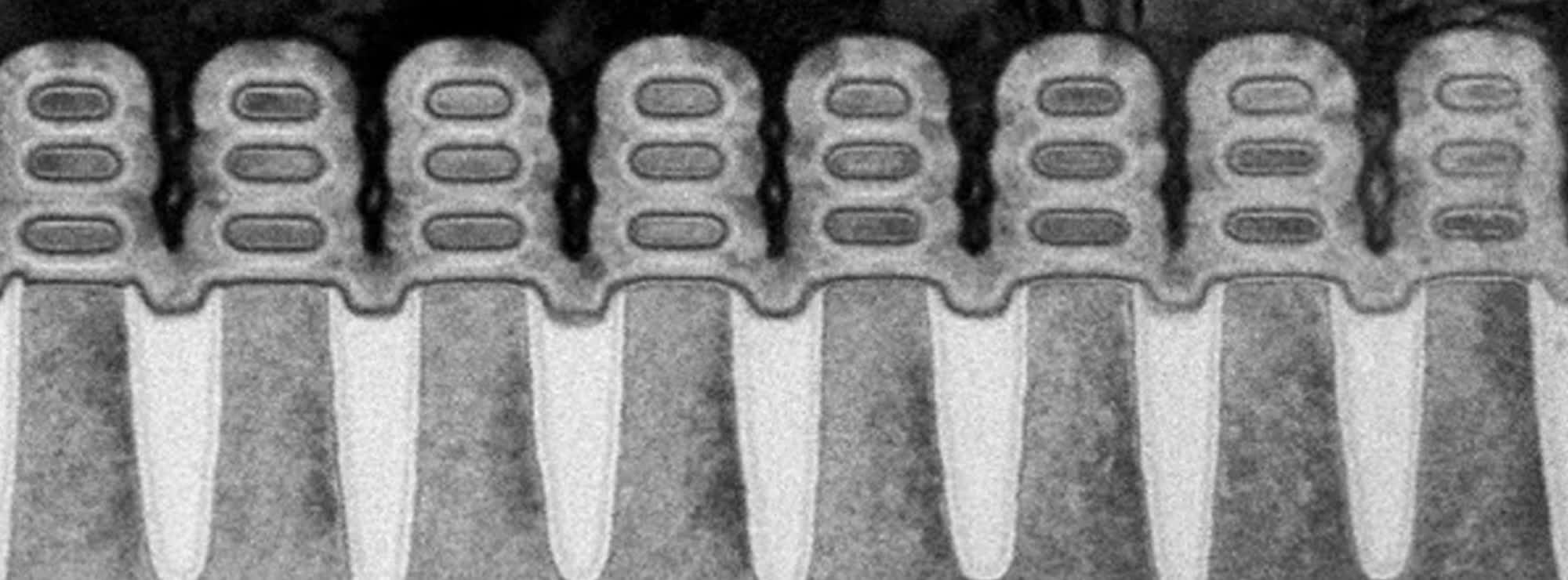

Essentiellement, MBC-FET est un FinFET tourné sur le côté avec la grille enroulée autour de nano-feuilles de silicium cultivées sur un substrat. Intel a une implémentation similaire basée sur des «nanorubans» prévue pour ses puces 2025, bien que ce calendrier puisse changer sous la nouvelle direction.

Dans tous les cas, il semble que FinFET est sur le point de disparaître, tandis que les fonderies devront adopter le GAA-FET pour une utilisation au-delà des nœuds de processus 3 nm. Ce n’est pas seulement le prochain transistor pour les puces avancées – c’est peut-être la seule option dans un avenir prévisible, avec quelques variations selon les fonderies. Les coûts sont également plus élevés, ce qui rend peu probable que de nombreuses fonderies puissent se permettre la transition.

À mesure que les choses évoluent, les fabricants peuvent utiliser des semi-conducteurs à haute mobilité comme le germanium, l’antimoniure de gallium et l’arséniure d’indium pour améliorer les performances, mais le GAA-FET pourrait être la dernière étape de la loi de Moore. Cela signifie que les fabricants devront faire preuve de créativité avec des emballages avancés et de nouvelles architectures de puces pour conserver la même cadence de progrès.