La grande image: Cette semaine, lors de l’événement annuel Hot Chips, un Pat Gelsinger enthousiaste a parlé du prochain chapitre de la conception de la microarchitecture chez Intel. Il s’agit de Foveros, une technologie de packaging 3D qui donnera à Intel un pied plus rapide dans un paysage de semi-conducteurs de plus en plus difficile.

Les processeurs Core de 13e génération d’Intel sont à l’horizon, mais ils ne devraient pas trop s’éloigner de leurs prédécesseurs en ce qui concerne la microarchitecture. Après tout, Intel utilise le même nœud Intel 7 que les processeurs Alder Lake, il n’y a donc pas grand-chose à se réjouir, sauf pour des horloges plus élevées et de meilleures capacités d’overclocking.

Pendant ce temps, Team Blue travaille sur une architecture beaucoup plus excitante appelée Meteor Lake, qui comportera une configuration de chiplet. Contrairement à son rival AMD, Intel a été plus réticent à s’éloigner des conceptions monolithiques de système sur puce et n’a jusqu’à présent mis en œuvre l’approche à plusieurs modules qu’avec des processeurs de serveur comme la famille Sapphire Rapids et des GPU d’accélération de calcul comme la gamme Ponte Vecchio.

Cela dit, la société est bien consciente que l’avenir des semi-conducteurs réside dans les architectures de puces système sur boîtier au lieu d’entasser plus de transistors sur une seule puce. À cette fin, Intel travaille avec des sociétés comme AMD, Arm, Samsung, Qualcomm, Google, TSMC et d’autres pour définir une nouvelle norme industrielle appelée Universal Chiplet Interconnect Express (UCIe). Cette décision ouvrira la voie aux fabricants d’appareils pour mélanger et assortir facilement les composants de différents fournisseurs.

Meteor Lake est l’occasion idéale pour Intel de commencer à tenir les promesses faites lorsque le PDG Pat Gelsinger a pris la barre. Un : il laissera AMD dans le rétroviseur, et deux : il rattrapera le silicium de la série M d’Apple. Gelsinger en a récemment parlé et plus encore à la Frites Chaudes 34 conférence, mettant en lumière la stratégie renouvelée de l’entreprise.

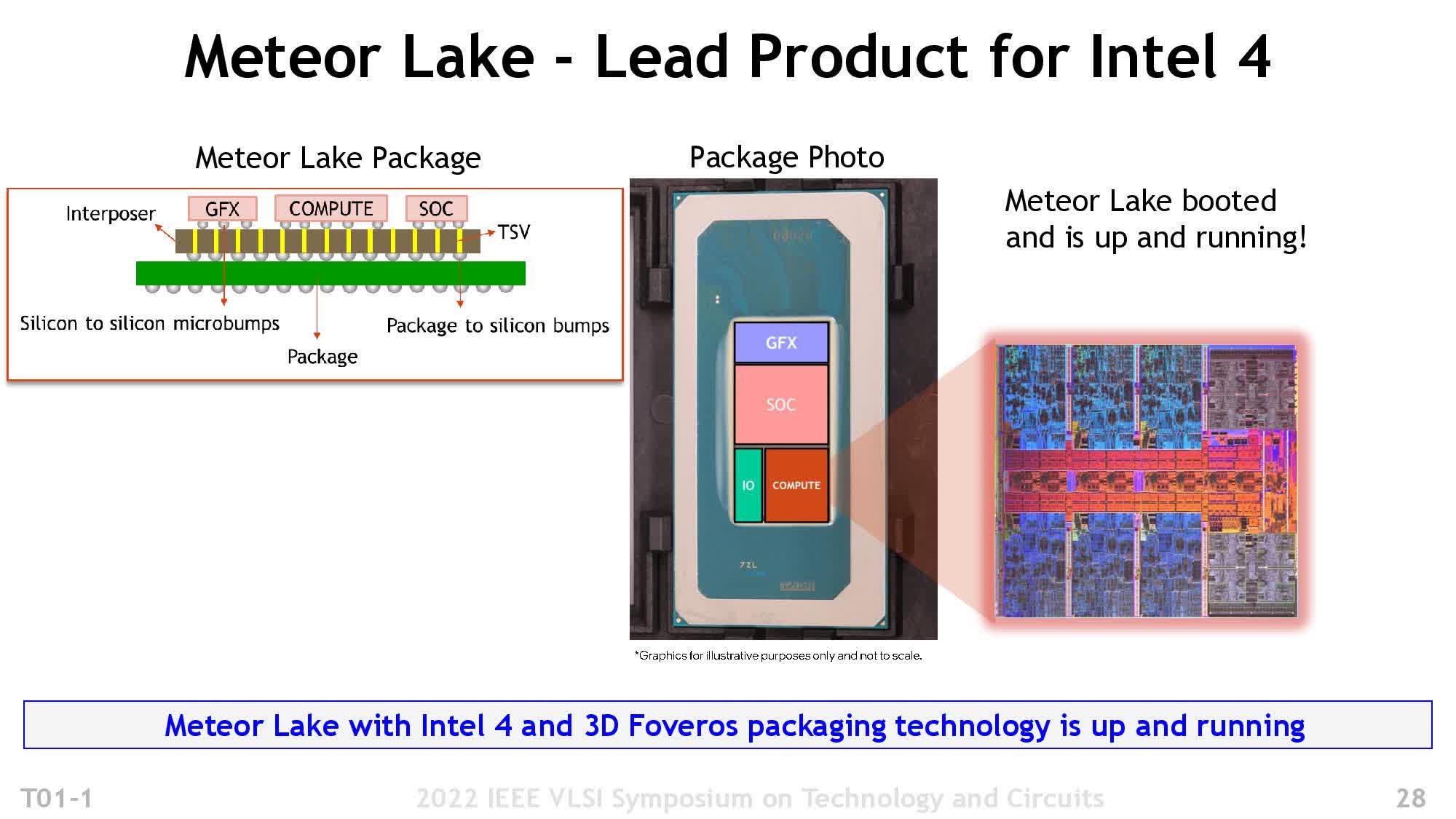

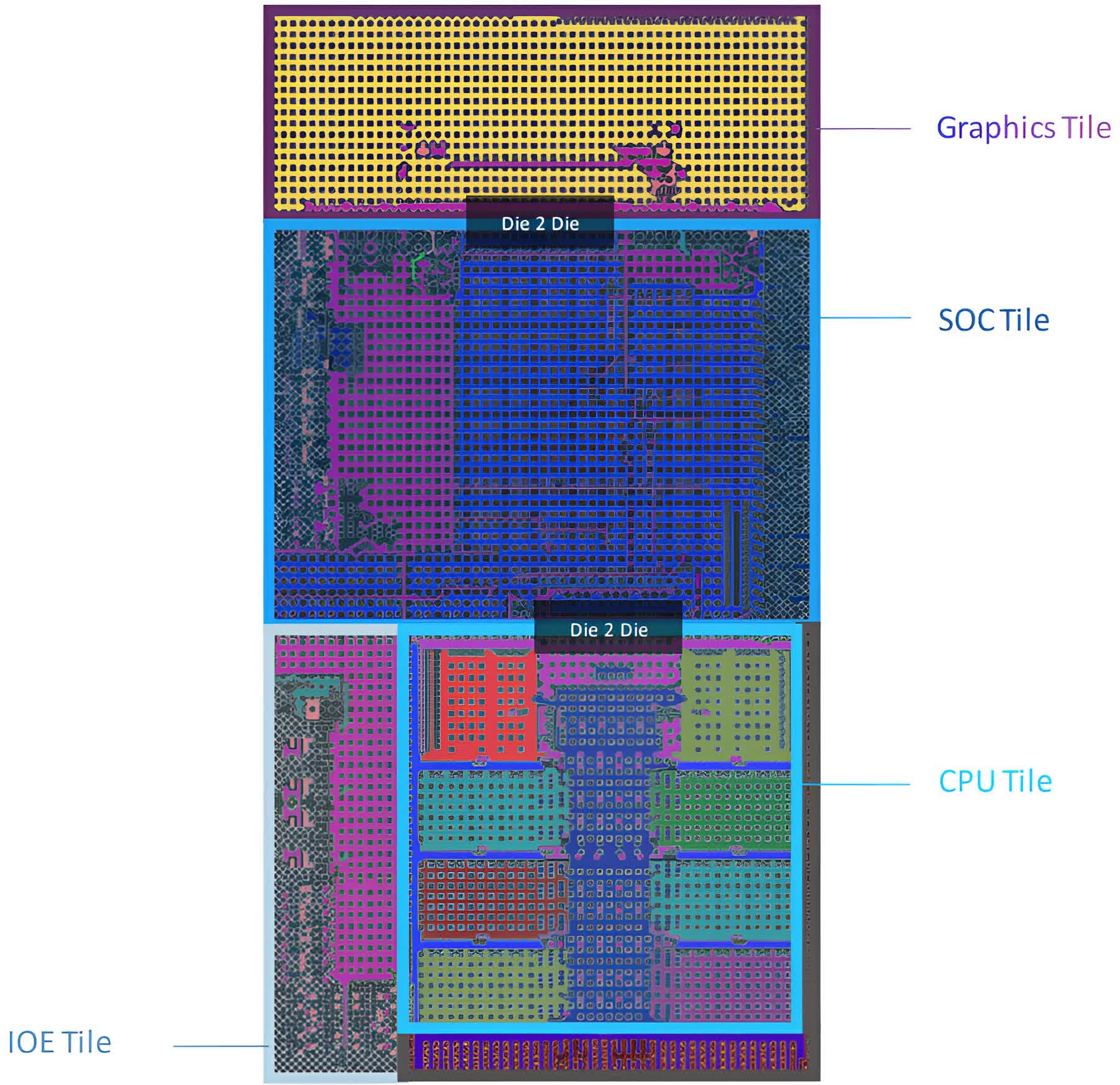

Chaque package Meteor Lake comportera quatre puces, dont une seule provenant d’une fonderie Intel. La société fabriquera le module principal à l’aide d’un nœud de processus Intel 4, tandis que TSMC fabriquera les trois autres, éventuellement sur trois nœuds différents.

Bien que cela puisse sembler une approche coûteuse et compliquée, la décomposition d’une grande conception monolithique en chiplets offre de meilleurs rendements et plus de flexibilité lors du choix de la technologie de processus optimale pour les tuiles CPU, GPU, I/O Expander et SoC. Ces modules sont liés à l’aide d’une technologie qu’Intel utilisera également pour les processeurs Arrow Lake et Lunar Lake – 3D Foveros.

Vous vous souviendrez peut-être qu’Intel a fait la première démonstration d’une technologie de conditionnement 3D pour les puces logiques il y a environ trois ans et demi. Une caractéristique clé de Foveros est la liaison face à face, puce sur puce, qu’il réalise à l’aide de minuscules bosses de 36 microns. Cette technique permet aux fabricants d’empiler les puces comme des pancakes pour de meilleures performances et une consommation d’énergie moindre.

L’interposeur Foveros de première génération double ou triple la bande passante par rapport à un interposeur en silicium et passe de conceptions de trois watts à un énorme kilowatt. Comme les processeurs Lakefield de courte durée, Intel fabrique cet interposeur en utilisant un processus 22FFL unique optimisé pour l’efficacité énergétique.

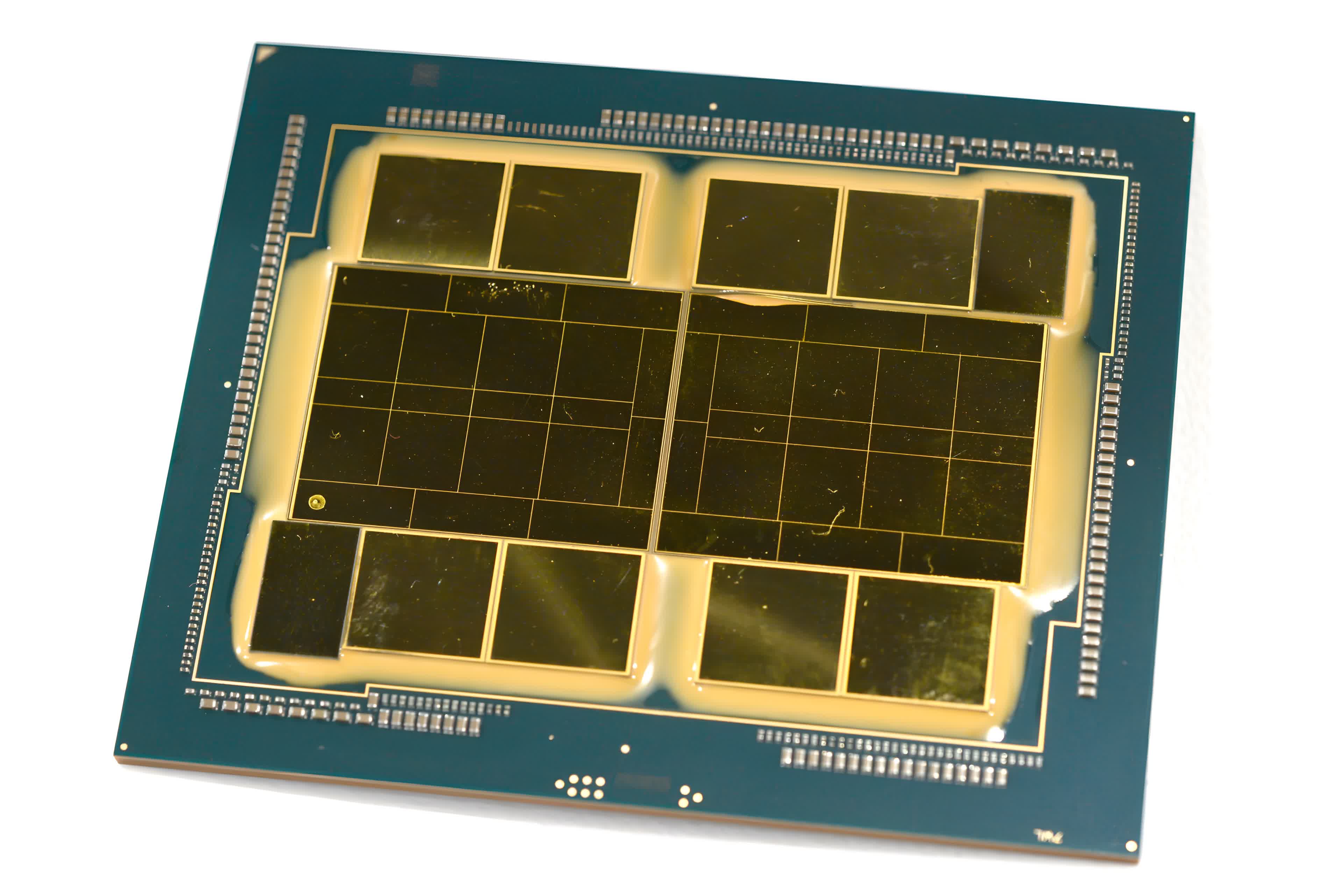

Il convient également de noter qu’Intel prévoit d’utiliser Foveros en conjonction avec sa technologie 2.5D, Embedded Multi-Die Interconnect Bridge (EMIB), utilisée dans ses familles de produits FPGA Stratix et Agilex pour connecter des matrices adjacentes sur un plan 2D. La société exploite déjà ces techniques de conditionnement dans ses processeurs Sapphire Rapids, que nous prévoyons d’expédier aux clients des centres de données plus tard cette année. Il en va de même pour les GPU Ponte Vecchio, qui seraient censés être 2,5 fois plus puissants que l’A100 de Nvidia si l’on se fie aux chiffres d’Intel.

Ponte Vecchio contient plus de 100 milliards de transistors sur 47 puces et peut pomper jusqu’à 52 téraflops de calcul FP32/FP64. Pourtant, Intel a des ambitions plus élevées pour emballer encore plus de puissance dans les futures conceptions utilisant Foveros et EMIB.

Gelsinger affirme que la société souhaite atteindre un billion de transistors dans un seul boîtier d’ici 2030, et qu’elle fait déjà des pas dans cette direction avec des technologies telles que Foveros Omni et Forveros Direct. En théorie, Intel pourrait éventuellement utiliser des interconnexions de liaison hybrides avec des bosses de 1 micron et mélanger plusieurs tuiles supérieures avec des bases produites sur différents nœuds de processus. Il s’attend à une fabrication en volume d’ici l’année prochaine.

Les consommateurs de Meteor Lake devraient bénéficier d’un matériel plus puissant à peu près au même prix malgré la complexité supplémentaire. Intel ne se lance que maintenant dans la fabrication en série de produits de consommation utilisant des emballages 3D Foveros. Cependant, la société est convaincue qu’elle peut fournir des processeurs qui coûtent le même prix ou moins par rapport aux alternatives monolithiques à puce unique.

Bien qu’Intel n’entre pas dans les détails des performances que nous pouvons attendre de la tuile d’interconnexion Foveros, on nous dit que cette technologie est conçue pour fonctionner à « plusieurs GHz », même dans une configuration passive. Il y a même des rumeurs selon lesquelles les processeurs de 14e génération intégreront des capacités de lancer de rayons, mais nous devrons attendre et voir. AMD a eu beaucoup de succès avec les conceptions de puces, il sera donc intéressant de voir à quel point Intel peut s’exécuter en suivant un itinéraire similaire.

De plus, la possibilité de mélanger et d’assortir les tuiles fabriquées sur des nœuds de processus matures et de pointe donne à Intel un avantage sur le front des services de fonderie, où il prévoit de progresser rapidement dans les années à venir. Team Blue peut tirer le meilleur parti de l’expertise EUV de TSMC tout en travaillant à l’intégration de plus de techniques EUV dans sa propre technologie de processus.

Crédit image : PCWatch