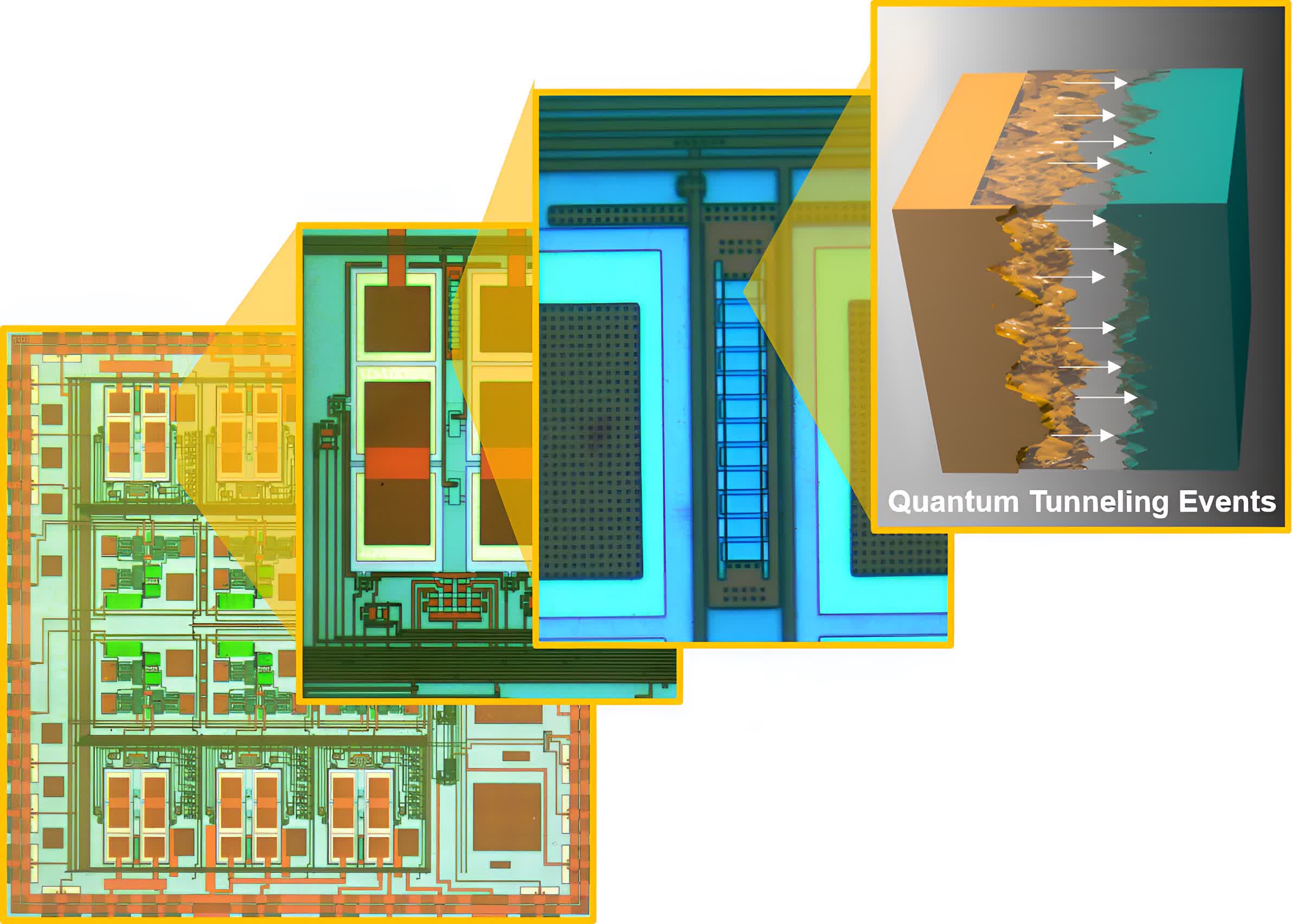

Pourquoi est-ce important: La loi de Moore est sous assistance respiratoire depuis un moment maintenant, mais elle n’est pas encore morte. Les fabricants de puces brûlent l’huile de minuit pour miniaturiser les conceptions de transistors, et une équipe de chercheurs en Chine a créé ce que l’on pense être le plus petit à ce jour.

Pendant plusieurs décennies, les scientifiques et les ingénieurs ont réduit les transistors au point que leurs plus infimes caractéristiques ne sont composées que de dizaines d’atomes. Depuis les premiers circuits intégrés dans les années 1950, le rythme de progression de la miniaturisation des transistors a suivi la loi de Moore, qui prévoyait que la densité de composants actifs dans les puces intégrées doublerait tous les deux ans.

Comme nombre de nos lecteurs le savent, les progrès dans cette direction se sont considérablement ralentis ces dernières années. La raison principale est que nous approchons rapidement des limites physiques de ce qui est possible avec les matériaux existants et les processus de fabrication les plus avancés dont nous disposons.

Plus précisément, nous ne pouvons pas fabriquer des grilles de transistors – qui contrôlent le flux de courant de la source au drain – beaucoup plus petites que 5 nm à cause de quelque chose appelé effet tunnel quantique qui les empêche de fonctionner comme prévu. Des matériaux comme le graphène et les nanotubes de carbone pourraient être essentiels pour rendre les transistors encore plus petits grâce à leurs propriétés physiques, mais passer de là à la construction de dispositifs fonctionnels prendra un certain temps.

Dans un papier publié cette semaine, des chercheurs chinois expliquent qu’ils ont créé un transistor avec la plus petite longueur de grille jamais signalée. Cette étape a été rendue possible en utilisant de manière créative le graphène et le bisulfure de molybdène et en les empilant dans une structure d’escalier à deux marches.

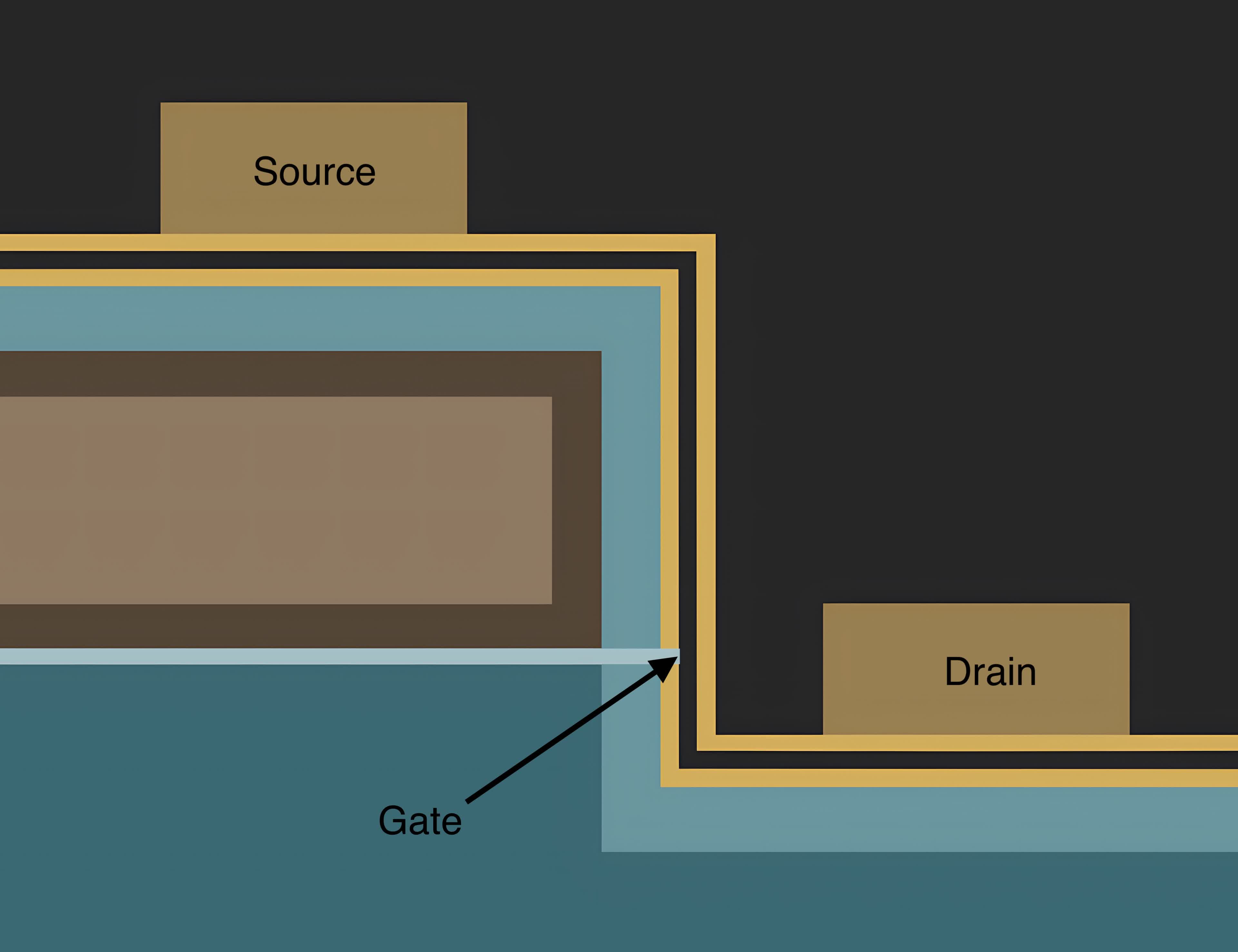

Sur la marche supérieure, vous avez la source, et sur la marche inférieure, vous avez le drain. Tous deux sont constitués d’un alliage de titane palladium séparé par la surface de l’escalier, qui est constitué d’une seule feuille d’un matériau semi-conducteur appelé bisulfure de molybdène, lui-même reposant sur une couche de dioxyde d’hafnium qui agit comme un isolant électrique.

L’intérieur de la marche supérieure est un sandwich littéral d’aluminium recouvert d’oxyde d’aluminium, qui repose sur une feuille de graphène, une seule couche d’atomes de carbone. L’oxyde d’aluminium agit comme un isolant électrique, à l’exception d’un petit espace dans la paroi verticale de l’étape supérieure, où la feuille de graphène est autorisée à entrer en contact avec le disulfure de molybdène. Toute la structure de l’escalier repose sur une épaisse couche de dioxyde de silicium.

L’astuce de cette conception est que le bord de la feuille de graphène est utilisé, ce qui signifie que lorsque la porte est réglée sur l’état « activé », elle ne mesure que 0,34 nm de large, soit essentiellement la largeur de la couche de graphène elle-même. Une autre caractéristique notable de ce « transistor à paroi latérale » est sa fuite de courant négligeable en raison d’une résistance à l’état bloqué plus élevée. Les fabricants pourraient tirer parti de cette qualité pour les applications à faible puissance. Mieux encore, il serait relativement facile à fabriquer, même si de nombreux prototypes nécessitaient un peu de tension pour être pilotés.

Lisez aussi: La machine EUV de nouvelle génération d’ASML donnera un nouveau souffle à la loi de Moore

Le chercheur de l’Université Tsinghua, Tian-Ling Ren, co-auteur de l’étude, a déclaré que cela pourrait être « le dernier nœud de la loi de Moore ». Il pense également qu’il est presque impossible de réduire la taille de la porte à moins de 0,34 nm.

Bien sûr, les chercheurs à l’origine du nouveau transistor ont seulement prouvé qu’un transistor fonctionnel pouvait être fabriqué à l’aide de matériaux minces à un atome sans inventer un nouveau procédé de positionnement de précision des couches requises. Construire de manière fiable des milliards de ces transistors à paroi latérale est encore un rêve lointain, mais constitue une étape critique dans cette direction, qui alimente l’espoir de dispositifs plus rapides et plus économes en énergie à l’avenir.

Entre-temps, Samsung, Intel et TSMC travaillent d’arrache-pied pour faire des transistors gate-all-around (GAA-FET) une réalité et normaliser les interconnexions pour les conceptions de puces.