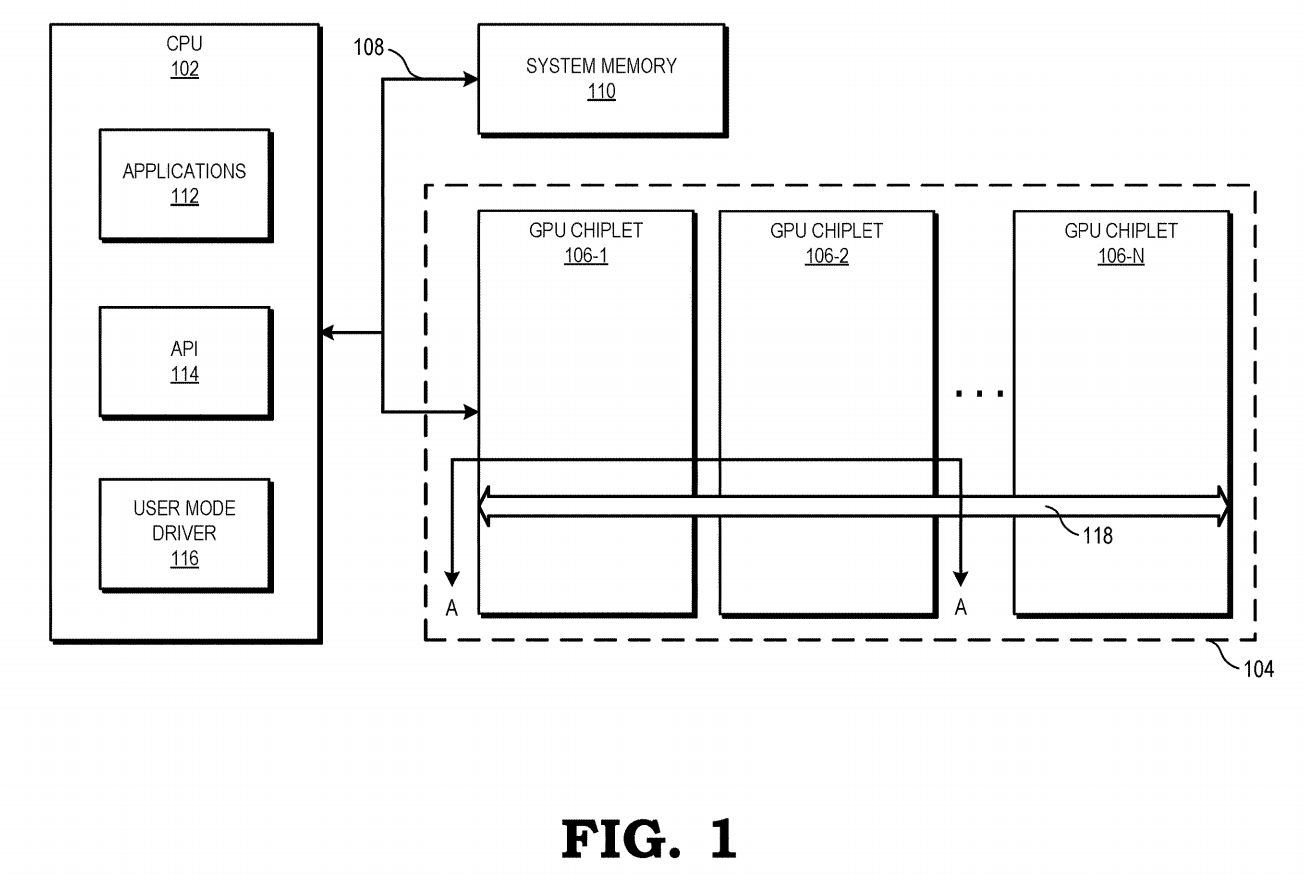

Quelque chose à espérer: AMD a publié son premier brevet sur les conceptions de GPU Chiplet. À la manière typique d’AMD, ils essaient de ne pas faire basculer le bateau. Les GPU Chiplet commencent tout juste à émerger. Intel a été franc sur son processus de développement et a confirmé l’utilisation de puces dans ses GPU discrets de première génération. Nvidia, bien que timide sur les détails, a publié de nombreux articles de recherche sur le sujet. AMD a été le dernier à tenir – ce qui ne fait qu’ajouter à l’intrigue.

Les puces, comme leur nom l’indique, sont des puces plus petites et moins complexes, destinées à fonctionner ensemble dans des processeurs plus puissants. Ils sont sans doute l’avenir inévitable de tous les composants haute performance et, dans certains cas, le présent réussi; L’utilisation par AMD des conceptions de processeurs à puce a été brillante.

dans le nouveau brevet daté du 31 décembre, AMD décrit un design de chiplet conçu pour imiter au plus près un design monolithique. Leur modèle hypothétique utilise deux puces connectées par un interposeur inactif à grande vitesse appelé réticulation.

Une connexion croisée se trouve entre le cache L2 et le cache L3 dans la hiérarchie de la mémoire. Tout ce qui se trouve en dessous, comme les cœurs et le cache L1 et le cache L2, est conscient de leur séparation de l’autre chiplet. Tout ce qui précède, y compris le cache L3 et la mémoire GDDR, est partagé entre les chiplets.

Cette conception est intéressante car elle est conventionnelle. AMD affirme que les unités de calcul peuvent accéder au cache de bas niveau sur d’autres chiplets presque aussi rapidement qu’elles peuvent accéder au cache de bas niveau local. Si cela s’avère vrai, le logiciel n’aura pas besoin d’être mis à jour.

On ne peut pas en dire autant des conceptions d’Intel et de Nvidia. Intel a l’intention d’utiliser deux nouvelles technologies, EMIB (pont d’interconnexion multi-pu embarqué) et Foveros. Ce dernier est un interposeur actif qui utilise des vias via silicium, ce qu’AMD déclare explicitement ne pas utilisation. La conception d’Intel permet au GPU d’héberger un cache accessible par le système qui alimente une nouvelle structure mémoire.

Nvidia n’a pas tout divulgué, mais a indiqué quelques directions à suivre. UNE document de recherche à partir de 2017, décrit une conception à quatre puces et une architecture prenant en charge NUMA (accès mémoire non uniforme) et tenant compte de la localité. Il expérimente également un nouveau cache L1.5, qui contient exclusivement les accès aux données à distance et est contourné lors des accès à la mémoire locale.

L’approche d’AMD peut sembler la moins imaginative, mais elle semble également pratique. Et si l’histoire a prouvé quelque chose, c’est que la convivialité pour les développeurs est un énorme avantage.

Vous trouverez ci-dessous des schémas supplémentaires du brevet.

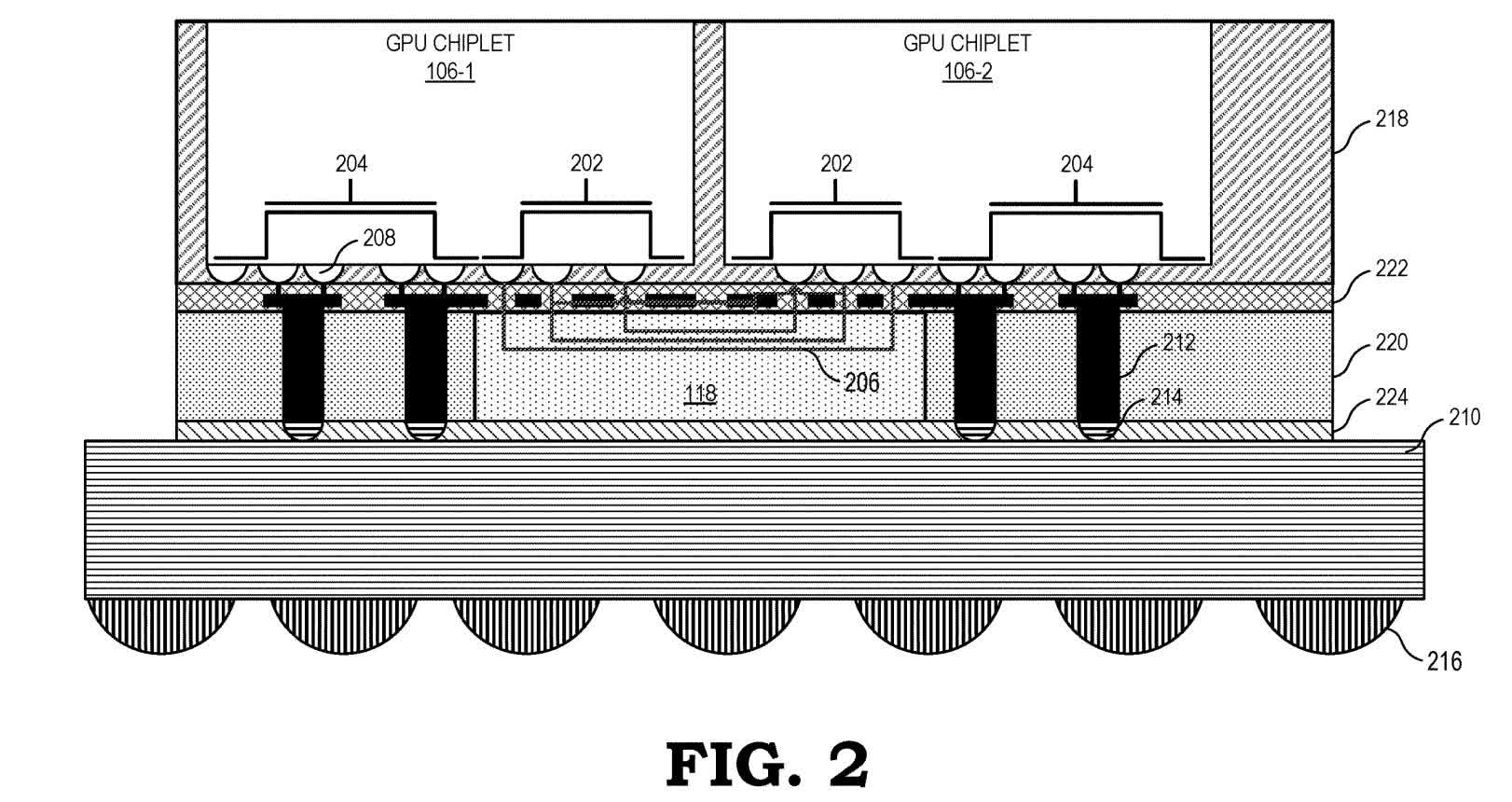

La figure 2 est une vue en coupe qui descend de deux puces à la carte de circuit imprimé. Les deux puces (106-1 et 106-2) sont empilées verticalement sur la réticulation passive (118) et utilisent des structures conductrices dédiées pour accéder aux traces de réticulation (206) et ensuite communiquer entre elles. Les structures conductrices non fixées à la réticulation (204) se connectent à la carte de circuit imprimé pour l’alimentation et d’autres signaux.

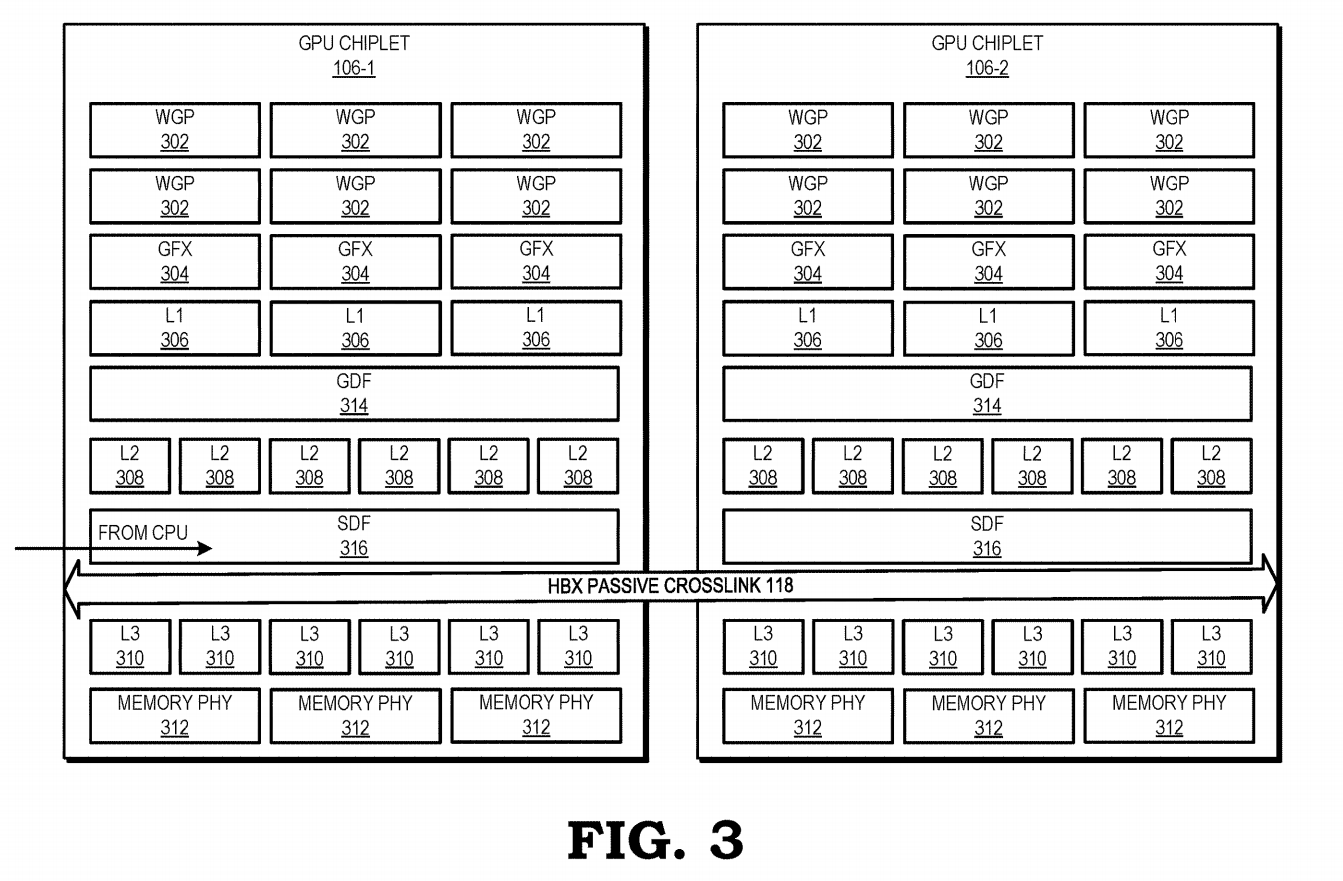

La figure 3 illustre la hiérarchie du cache. Les WGP (processeurs de groupe de travail) (302), qui sont des collections de cœurs de shader, et les GFX (unités fonctionnelles fixes) (304), qui sont des processeurs dédiés à des fins singulières, se connectent directement au cache L1 d’un canal (306). Chaque chiplet contient plusieurs banques de cache L2 (308) qui sont adressables individuellement et également cohérentes dans un seul chiplet. Chaque chiplet contient également plusieurs banques de cache L3 cache (310) cohérentes sur l’ensemble du GPU.

Le GDF (Graphics Data Fabric) (314) connecte les banques de cache L1 aux banques de cache L2. Le SDF (scalable data fabric) (316) combine les banques de cache L2 et les connecte au crosslink (118). Le crosslink se connecte aux SDF sur tous les chiplets, ainsi qu’aux banques de cache L3 sur tous les chiplets. Les voies de mémoire GDDR (écrites comme mémoire PHY) (312) se connectent aux banques de cache L3.

À titre d’exemple, si un WGP sur un chiplet nécessitait des données d’une banque GDDR sur un autre chiplet, ces données seraient envoyées via une banque de cache L3, puis via la liaison croisée vers un SDF, puis vers une banque L2, et enfin, via un GDF à une banque L1.

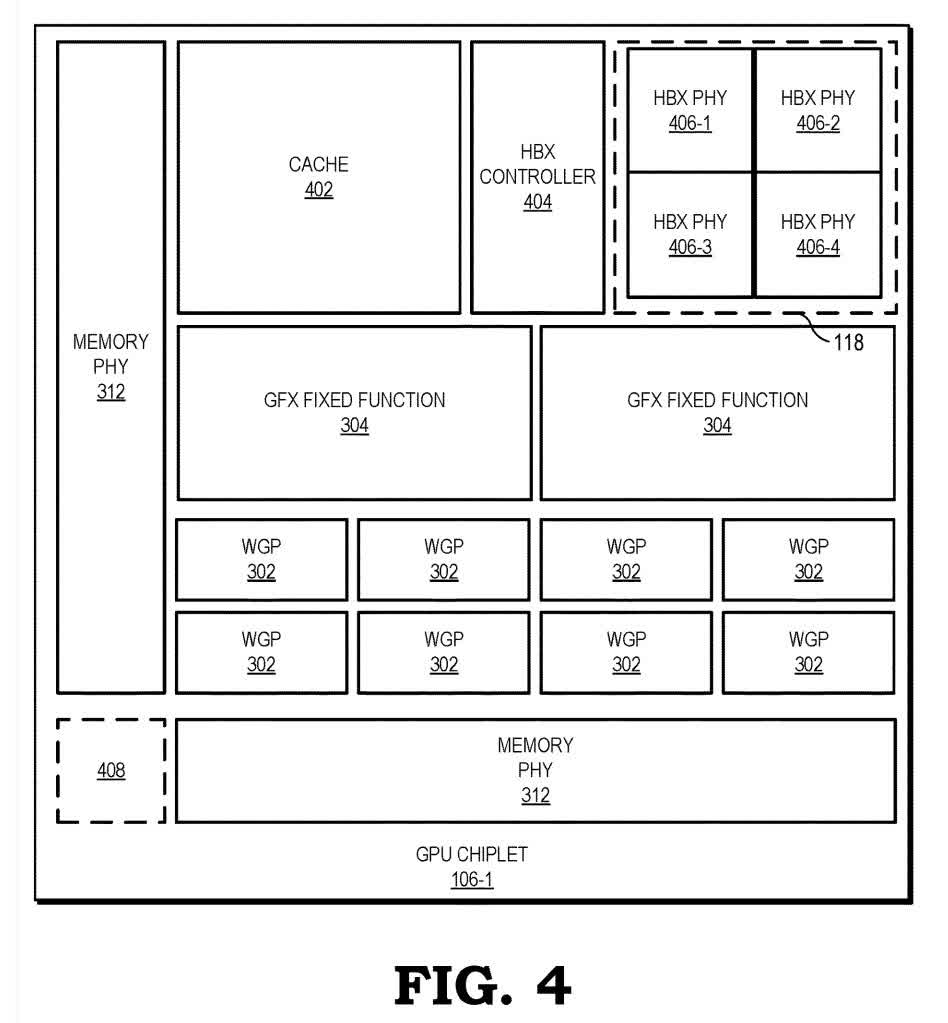

La figure 4 est une vue à vol d’oiseau d’un chiplet. Il montre plus précisément les emplacements potentiels et les échelles de divers composants. Le contrôleur HBX (404) gère la réticulation, à laquelle le chiplet est connecté par des conducteurs HBX PHY (406). Le petit carré dans le coin inférieur gauche (408) est une connexion supplémentaire potentielle à la réticulation pour connecter plus de puces.