Samsung a déclaré jeudi qu’il était sur la bonne voie pour démarrer la production à haut volume en utilisant son 3GAE (3 nm-class gate all-around early) processus de fabrication ce trimestre (c’est-à-dire dans les semaines à venir). L’annonce marque non seulement la première technologie de fabrication de classe 3 nm de l’industrie, mais également le premier nœud à utiliser des transistors à effet de champ tout autour de la porte (GAAFET).

« Améliorer le leadership technologique grâce à la première production de masse au monde du procédé GAA 3-nano », a déclaration [PDF] par Samsung lit.

Fonderie Samsung Technologie de processus 3GAE est le premier processus de la société à utiliser des transistors GAA, que Samsung appelle officiellement les transistors à effet de champ à canaux multiponts (MBCFET).

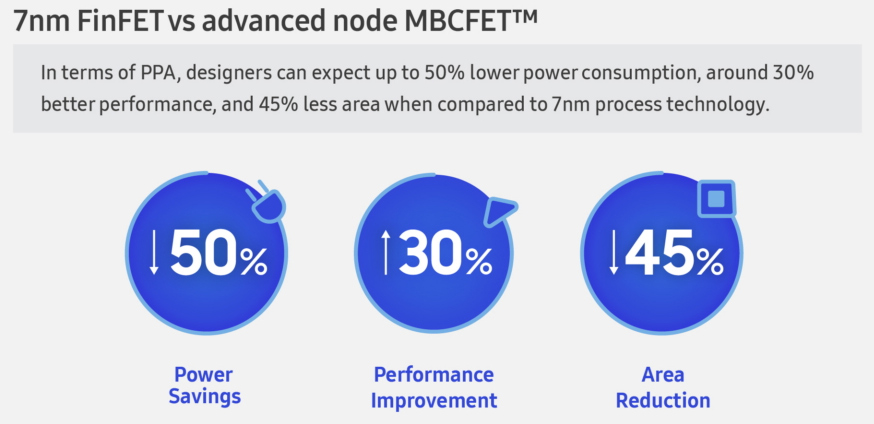

Samsung a officiellement présenté ses nœuds 3GAE et 3GAP il y a environ trois ans. Lorsque l’entreprise a décrit son Puce SRAM GAAFET 256 Mo produit à l’aide de sa technologie 3GAE, il a fait un certain nombre de revendications. Samsung a déclaré que le processus permettrait une augmentation des performances de 30%, une réduction de la consommation d’énergie de 50% et une densité de transistors jusqu’à 80% supérieure (y compris un mélange de transistors logiques et SRAM). Il reste à voir comment la combinaison réelle de performances et de consommation d’énergie se jouera pour Samsung.

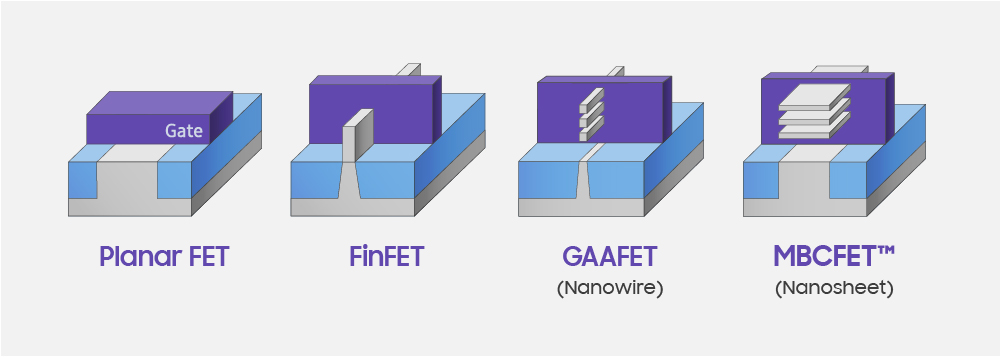

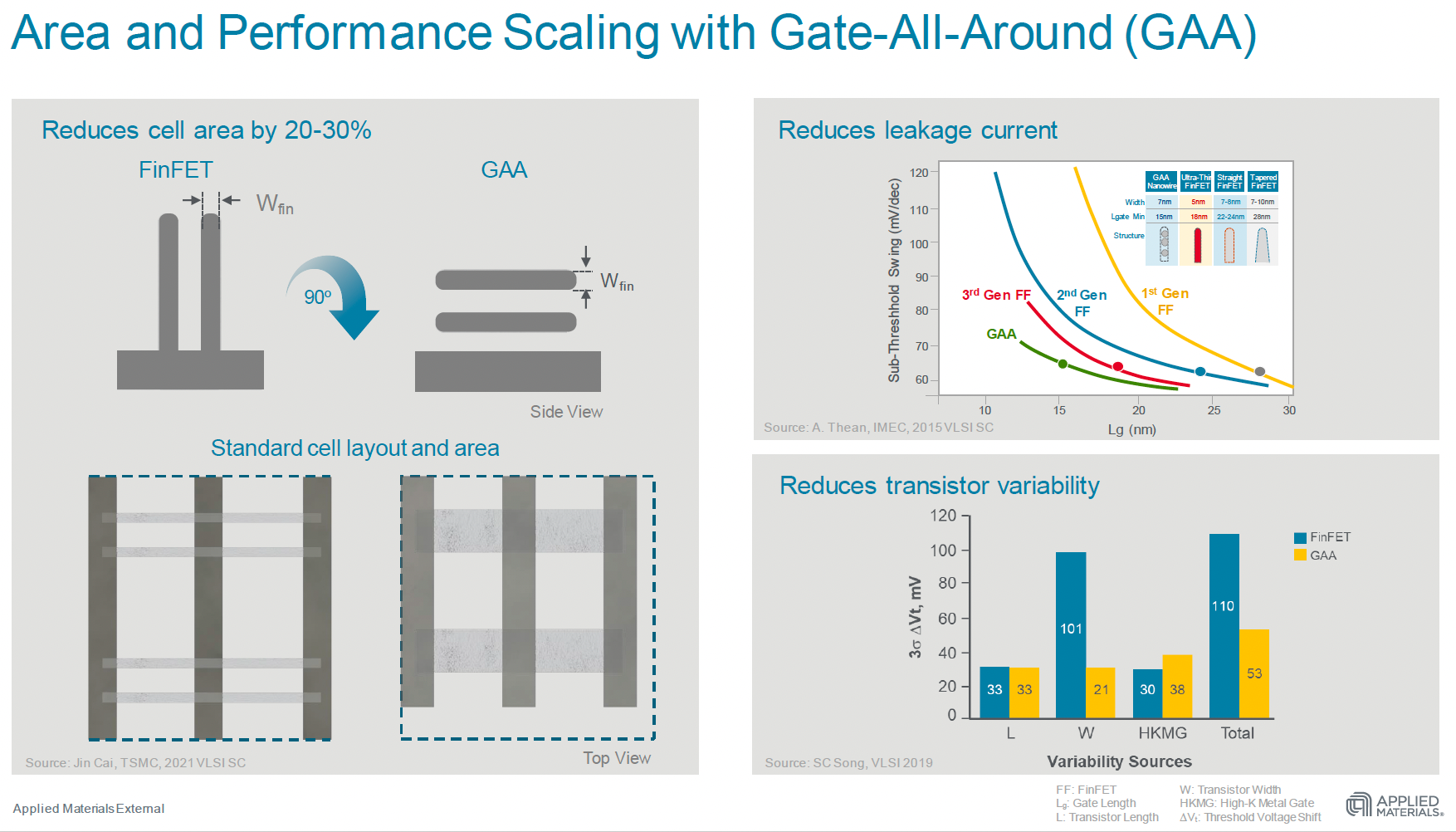

En théorie, les GAAFET présentent un certain nombre d’avantages par rapport aux FinFET actuellement utilisés. Dans les transistors GAA, les canaux sont horizontaux et sont entourés de grilles. Les canaux GAA sont formés par épitaxie et élimination sélective des matériaux, ce qui permet aux concepteurs de les régler avec précision en ajustant la largeur du canal du transistor. La haute performance est obtenue via des canaux plus larges, la faible puissance via des canaux plus étroits. Une telle précision réduit considérablement le courant de fuite des transistors (c’est-à-dire réduit la consommation d’énergie) ainsi que la variabilité des performances des transistors (en supposant que tout fonctionne bien), ce qui signifie un délai de rendement plus rapide, un délai de mise sur le marché et des rendements améliorés. En outre, les GAAFET promettent de réduire la surface cellulaire de 20 % à 30 %, selon une présentation récente de Matériaux appliqués.

En parlant d’Applied, son système IMS (Integrated Materials Solution) à système de vide poussé récemment introduit pour former l’empilement d’oxyde de grille est destiné à relever un défi majeur de la fabrication de transistors GAA, un espace très mince entre les canaux et la nécessité de déposer le multi- couche d’oxyde de grille et empilements de grille métallique autour des canaux en très peu de temps. Le nouvel outil AMS d’Applied Materials peut déposer un oxyde de grille d’une épaisseur de seulement 1,5 angström en utilisant le dépôt de couche atomique (ALD), des étapes thermiques et des étapes de traitement au plasma. La machine hautement intégrée effectue également toutes les étapes de métrologie nécessaires.

Le 3GAE de Samsung, étant une technologie de fabrication « précoce » de classe 3 nm, le 3GAE sera principalement utilisé par Samsung LSI (la branche de développement de puces de Samsung) et peut-être un ou deux des autres clients alpha de SF. En gardant à l’esprit que le LSI de Samsung et d’autres premiers clients de SF ont tendance à construire des puces en très gros volumes, attendez-vous à ce que la technologie 3GAE soit utilisée assez largement, en supposant que les rendements et les performances de ces produits répondent aux attentes.

La transition vers une toute nouvelle structure de transistor est généralement un risque car elle implique un tout nouveau processus de fabrication ainsi que de tout nouveaux outils. Les autres défis sont les nouvelles méthodologies de placement, les règles de plan d’étage et les règles de routage qui sont introduites par tous les nouveaux nœuds et traitées par le nouveau logiciel d’automatisation de la conception électronique (EDA). Enfin, les concepteurs de puces doivent développer une toute nouvelle IP, ce qui coûte cher.