introduction

Signe des temps, le patron de Nvidia, Jen-Hsun Huang, a dévoilé les tout nouveaux graphiques de la série GeForce RTX 30 dans nul autre que sa cuisine. Sur la base de l’architecture Ampere qui a fait ses débuts dans l’espace du datacenter avec le GPU A100, Nvidia estime avoir doublé les performances de la dernière génération. De nobles revendications en effet.

La série GeForce 30 est initialement représentée par les RTX 3070, RTX 3080 et RTX 3090 premium. Le lancement est échelonné de sorte que le RTX 3080 est disponible à partir d’aujourd’hui, le champion RTX 3090 le 24 septembre et le RTX 3070 le 15 octobre. Alors, approfondissons ce qu’est Ampère, comment cela se manifeste dans le RTX 3080, puis évaluons la validité des affirmations de performances explosives de Nvidia.

Architecture Ampère

Ampère est une évolution de l’architecture Turing qui alimente les cartes des séries 20 et 16. Il est plus logique de l’examiner dans sa forme la plus complète, puis de se concentrer sur les améliorations apportées par Nvidia par rapport aux générations précédentes.

Voici le schéma synoptique de haut niveau habituel de la version de jeu complète d’Ampère. Connu sous le nom de GA102, c’est une bête de puce, comprenant 28,3 milliards de transistors sur une matrice de 628,3 mm² fabriquée selon le processus personnalisé 8 nm de Samsung. La décision de ne pas opter pour le 7 nm de TSMC est curieuse étant donné la relation de longue date de Nvidia avec la fonderie, mais le processus de pointe de Samsung a une densité de transistors similaire à celle du 7 nm populaire de TSMC, de sorte que les GPU résultants auraient été de taille similaire dans tous les cas.

Nvidia fait fonctionner ces transistors en entassant plus à peu près tout ce qui compte pour un GPU grand public. La matrice GA102 complète a 10 752 cœurs, 84 cœurs RT, 336 cœurs Tensor, plus de cache, plus de bande passante mémoire et une connectivité PCIe 4.0. Pourtant, une telle puce n’existe pas. Bien que RTX 3090 et RTX 3080 soient connus pour utiliser GA102, aucun des deux n’utilise sa capacité complète, laissant suffisamment de place pour un GPU RTX Titan entièrement activé sur toute la ligne.

Zoomer sur le silicium GA102 révèle que Nvidia héberge 84 multiprocesseurs (SM) en streaming regroupés en groupes de 12 au sein d’un cluster de traitement graphique (GPC). Ce sont ces SM, comme les générations précédentes, où se fait l’essentiel du travail. Nvidia s’efforce d’améliorer le débit et l’efficacité de chaque SM par rapport à son prédécesseur immédiat tout en s’intégrant davantage à la conception globale en adoptant un processus de fabrication plus petit. Ampère réussit sur les deux fronts.

Agrandissement du SM et déconnexion du ROP

En vous concentrant d’abord sur la rastérisation, vous vous souviendrez peut-être que Turing de dernière génération avait 64 cœurs FP32, également appelés cœurs Cuda, par SM, soit exactement la moitié de l’architecture Pascal qui l’a précédé. Nvidia a plutôt choisi d’imprégner le SM d’un chemin de données dédié pour les opérations sur les entiers. La raison de cette exécution simultanée de FP et INT résidait dans la façon dont les jeux modernes utilisent chaque type – 36 INT pour 100 FP – et ainsi avoir un chemin de données INT dédié libère les cœurs FP32 pour se concentrer sur ce qu’ils font le mieux – flottant- calculs de points. En Pascal, par exemple, chaque fois qu’une instruction entière est exécutée, les cœurs FP32 à double usage ne peuvent rien faire d’autre – ce sont des nombres flottants ou des entiers.

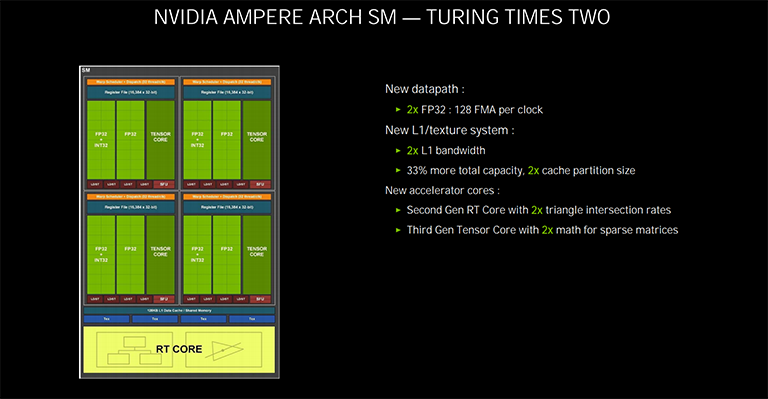

Ampère fait les choses différemment dans le SM. Maintenant, comme Turing, il y a 64 cœurs FP32 dédiés, répartis en quatre partitions de 16. Le grand changement est que le deuxième chemin de données, vu à gauche sur l’image, n’est pas limité au travail INT. Il peut également exécuter FP au besoin. Il est important de comprendre que ce deuxième chemin de données exécute INT ou FP, et non les deux en même temps. Cette nouvelle disposition signifie en fait que chaque SM a 64 cœurs FP32 Cuda et 64 autres pouvez exécutez FP32 ou INT.

Le résultat est que chaque Ampère SM a exactement le double de la capacité FP32 de Turing, et c’est pourquoi vous voyez des chiffres TFLOPS aussi surprenants lorsque vous parcourez les spécifications. Nous avons établi que les jeux n’exécutent pas tout le temps FP32; il y a un réel besoin de traitement INT, donc même si une carte basée sur Ampère peut avoir le double du TFLOPS d’un Turing leader, ce ne sera pas deux fois plus rapide. Le taux de FLOP maximal équivaut à évaluer les performances d’une voiture sur la seule puissance du moteur; c’est important, bien sûr, mais ce n’est pas le seul facteur qui compte.

Avoir plus de grognement dans chaque SM nécessite également d’augmenter les niveaux de cache. Par rapport à Turing, Ampere double le cache de données L1 à 128 Ko et double également la bande passante de la mémoire partagée à 128 octets par horloge. Nourrissez la bête … et tout ça.

Dans un autre mouvement qui parle d’efficacité, Nvidia déplace les sorties de rendu (ROP) d’être liées au cache L2 et au contrôleur de mémoire vers l’intérieur du GPC, à un taux de 16 par cluster. Cette déconnexion favorable signifie qu’Ampère peut augmenter le nombre de ROP par rapport à l’interface mémoire. À titre d’exemple, la génération Turing avait un maximum de 96 ROP à partir d’une interface de 384 bits. C’est maintenant augmenté à 112 (7×16) pour la même largeur. Pratique pour les travaux anti-aliasing.

Enfin, ceux qui s’intéressent aux capacités de double précision (FP64) de l’Ampère grand public doivent savoir qu’il existe deux cœurs FP64 dédiés par SM, soit exactement 1 / 64ème de FP32. Le rapport définit également les performances FP64 sur une base GPU par GPU, donc si une carte a, disons, 30 TFLOPS de FP32, elle aura 469 GFLOPS de FP64.

Suppression des goulots d’étranglement RT et amélioration du flou de mouvement

Les principales avancées de Turing portent sur l’introduction de blocs de traitement dédiés au raytracing et aux réseaux neuronaux (Tensor cores, DLSS). Ampère, naturellement, les améliore de plusieurs manières. Prenons d’abord les cœurs RT (raytracing).

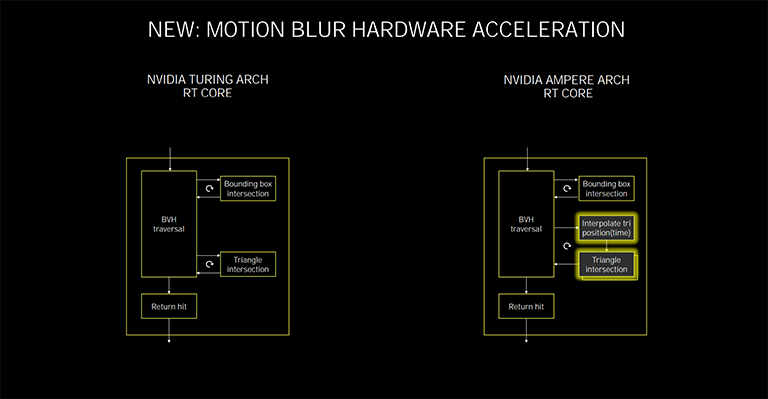

Comme auparavant, Nvidia investit de l’espace silicium dans des blocs RT à fonction fixe qui éliminent cette charge spécifique des unités SM. C’est le travail du noyau RT de calculer quels rayons lumineux doivent être dessinés en effectuant des tests de hiérarchie des volumes englobants (BVH) et d’intersection triangulaire. Le résultat est un succès ou un échec, et s’il s’agit du premier, il est renvoyé à l’unité SM pour faire son travail. En attendant, l’unité SM poursuit ses opérations habituelles de tramage.

Le noyau RT d’Ampère fonctionne de la même manière fondamentale que celui de Turing, mais ajoute deux fonctionnalités importantes pour des performances améliorées. Le premier est la présence d’une deuxième unité pour effectuer les tests d’intersection triangulaire, comme indiqué en bas à droite. Selon Nvidia, le noyau RT de Turing avait généralement des taux d’intersection de boîte englobante très solides, mais les taux d’intersection du triangle, à la fin du flux, avant d’être renvoyés au SM, présentaient souvent un goulot d’étranglement qui ralentissait l’ensemble du processus. Le doublement littéralement conduit à une meilleure efficacité RT. En termes simples, pour la même charge de travail RT, sur le même nombre de cœurs, Ampère devrait être plus rapide que Turing.

Notez la case ci-dessus? Position d’interpolation triangulaire. C’est une nouvelle fonctionnalité implémentée pour accélérer le lancer de rayons pour le flou de mouvement. En termes simples, le calcul du taux d’intersection rayon / triangle sur une scène régulière est relativement simple – le rayon frappe le triangle ou non – mais l’ajout de flou de mouvement dans le mélange le rend plus compliqué car le noyau RT tente de calculer les intersections temporellement. En d’autres termes, pour un éclairage RT précis sur les scènes de flou de mouvement, le matériel doit comprendre que chaque rayon existe à un moment différent. C’est là que ce matériel entre en jeu, et Nvidia dit qu’il offre jusqu’à 8 fois la traversée des rayons de Turing dans cette fonctionnalité de cas d’angle.