L’un des principaux moteurs de l’industrie des semi-conducteurs est la croissance des appareils toujours connectés qui nécessitent du silicium à l’intérieur, que ce soit pour le calcul, la communication ou le contrôle. L’ère de «l’Internet des objets», en fonction de la personne à qui vous parlez, va s’étendre à plusieurs milliards d’appareils et, par la suite, à plusieurs milliards de dollars d’opportunités. Afin de stimuler ce segment, les fonderies de semi-conducteurs ont développé des technologies de nœuds de processus à faible consommation et rentables pour leurs clients afin de les aider à atteindre un nouveau niveau d’efficacité énergétique et des implémentations à faible coût. Le tout nouveau processus de TSMC ciblant ce marché a été annoncé lors de son Symposium technologique 2020 et s’appellera N12e.

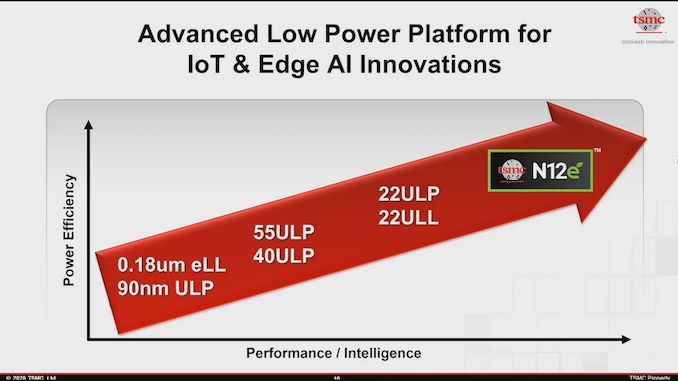

La feuille de route de TSMC pour ses plates-formes à faible puissance s’est centrée sur les technologies de nœuds de processus populaires optimisées pour une faible puissance et de faibles fuites. Au cours de la dernière décennie, TSMC a proposé des versions basse consommation de 90 nm, 55 nm, 40 nm et 22 nm, chaque génération offrant des zones de matrice plus petites et une puissance inférieure, ainsi que d’autres optimisations de conception spécifiques à chaque besoin. Celles-ci étaient toutes des technologies planaires, mais le nouveau nœud de processus N12e est la prochaine génération et basé sur les FinFET.

Les FinFET sont, dans un scénario comparable, plus complexes à construire que les transistors plans et devraient donc naturellement coûter plus cher à produire. Cependant, les technologies FinFET offrent également des avantages en termes d’évolutivité et de puissance, ce qui intéresse ce marché. Plutôt que d’introduire les FinFET plus tôt dans le cycle, TSMC a attendu quelques générations avant de pouvoir déployer ses conceptions FinFET les plus avancées sur ce marché, pour faciliter la transition avec les avantages qu’une conception la plus optimisée pourrait apporter.

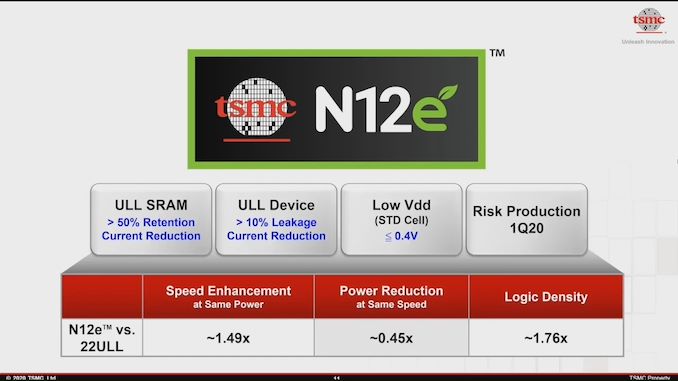

Dans N12e par rapport à 22ULL, TSMC promet une augmentation de 1,49x de la fréquence à iso-puissance, ou une réduction de 55% de la puissance à iso-vitesse. Cela s’accompagne également d’une augmentation de 1,76x de la densité logique et d’une bibliothèque de cellules basse tension spécialisée capable de 0,4 volts. Cela étend la gamme des offres de nœuds de processus IoT de TSMC à une fourchette de puissance inférieure, tout en offrant un meilleur profil de performance à toutes les autres puissances.

N12e associe la technologie du processus 16 nm de TSMC et l’associe aux améliorations et à l’expérience de 12FFC +, qui ont toutes deux été largement utilisées dans le calcul haute performance. TSMC estime que l’intégration de cela à ses connaissances à très faibles fuites aidera à activer la prochaine génération d’appareils IoT Edge compatibles 5G, en fournissant des routes à faible puissance aux accélérateurs d’IA pour la reconnaissance vocale, la surveillance de la santé et la vision industrielle.

Le principal concurrent de N12e serait la plate-forme GlobalFoundries 12FDX, qui repose sur la technologie FD-SOI 12 nm de GF, avec des déclarations de meilleure consommation d’énergie et de coût inférieur à celui des conceptions FinFET équivalentes. Cependant, malgré les discussions sur 12 FDX pendant plusieurs années (et les nouvelles du nouveau support MRAM et autres), il n’y a pas eu de succès de conception publique pour le processus.

On ne sait pas quand TSMC commencera à prendre des commandes pour sa plate-forme N12e, mais la société a déclaré qu’elle était « enthousiasmée » par la prochaine génération de produits construits dessus.

La source: TSMC N12e