La génération actuelle de matériel quantique a été appelée « NISQ »: processeurs quantiques bruyants à échelle intermédiaire. « échelle intermédiaire » fait référence à un nombre de qubits qui se compte généralement par dizaines, tandis que « bruyant » fait référence au fait que les qubits actuels produisent fréquemment des erreurs. Ces erreurs peuvent être causées par des problèmes de réglage ou de lecture des qubits ou par la perte d’état du qubit lors des calculs.

À long terme, cependant, la plupart des experts s’attendent à ce qu’une certaine forme de correction d’erreur soit essentielle. La plupart des schémas de correction d’erreurs impliquent la distribution des informations logiques d’un qubit sur plusieurs qubits et l’utilisation de qubits supplémentaires pour suivre ces informations afin d’identifier et de corriger les erreurs.

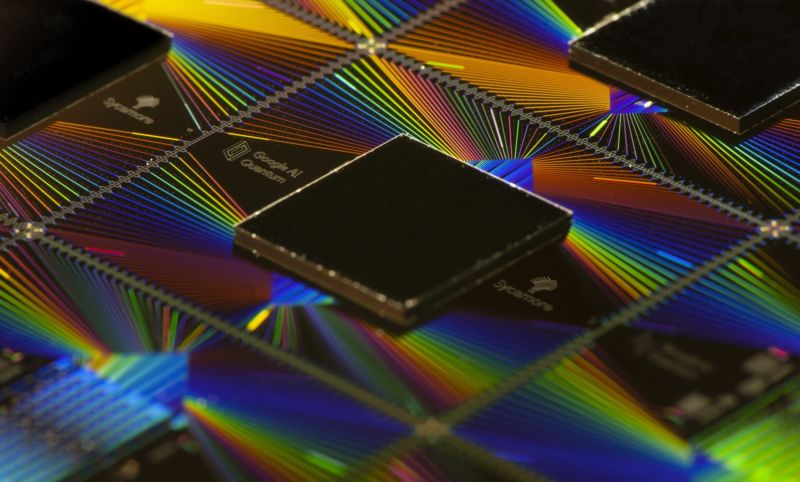

De retour quand nous rendu visite aux gens du groupe d’informatique quantique de Google, ils ont mentionné que la disposition de leur processeur a été choisie car elle simplifie la mise en œuvre de la correction d’erreurs. À présent, l’équipe exécute deux schémas de correction d’erreurs différents sur le processeur. Les résultats montrent que la correction d’erreur fonctionne clairement, mais nous aurons besoin de beaucoup plus de qubits et d’un taux d’erreur inhérent inférieur avant que la correction ne soit utile.

Géométrie variable

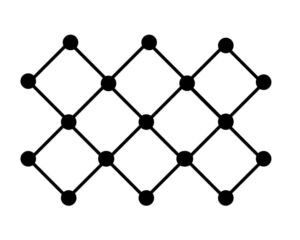

Dans tous les processeurs quantiques, les qubits sont agencés avec des connexions à leurs voisins. Il existe de nombreuses façons d’organiser ces connexions, avec des limites imposées par les qubits qui doivent se trouver à la périphérie du réseau et donc avoir moins de connexions. (La plupart des processeurs avec un nombre de qubits plus élevé ont tendance à avoir une ou plusieurs connexions inactivées, soit en raison d’un problème de fabrication, soit d’un taux d’erreur élevé.)

John Timmer

Google a choisi une géométrie dans laquelle tous les qubits internes sont connectés à quatre voisins. Pendant ce temps, ceux sur le bord n’ont qu’une paire de connexions. Vous pouvez voir cette disposition de base sur la droite.

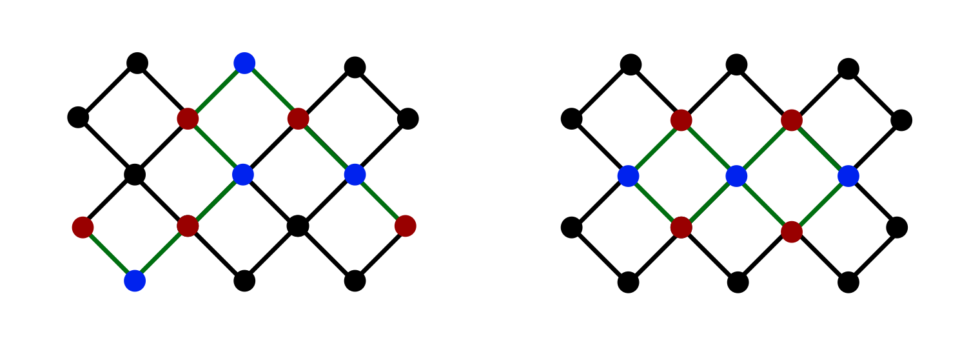

Les deux schémas de correction d’erreurs sont schématisés ci-dessous. Dans les deux diagrammes, les données (un seul qubit logique) sont réparties sur les qubits représentés par les points rouges. Les points bleus sont des qubits qui peuvent être mesurés pour vérifier les erreurs et manipulés pour les corriger. Pour faire une analogie avec les bits standard, vous pouvez considérer les bits bleus comme un moyen de vérifier la parité des bits voisins et, en cas de problème, d’identifier le qubit le plus susceptible d’avoir souffert du problème.

Dans la première configuration, à gauche, les qubits de mesure et de stockage alternent le long d’une chaîne linéaire, la longueur de la chaîne étant limitée uniquement par le nombre de qubits dans le processeur (qui est plus grand que le schéma illustré ici). Chaque qubit de mesure suit ses deux voisins ; si l’un ou l’autre souffre d’une seule erreur, les mesures de ce bit le détecteraient. (Ceci étant des qubits, il y a plus d’une erreur possible, et ce schéma échouera si deux types d’erreur différents se produisent simultanément.)

John Timmer

Le deuxième schéma, à droite, nécessite une géométrie plus spécifique, de sorte que la configuration est plus difficile à répartir sur de plus grandes parties du processeur. Il est plus difficile de déterminer lequel des qubits de données est en cause lorsqu’une erreur est détectée. Les calculs doivent être rejetés plutôt que corrigés lorsque des problèmes sont détectés. L’avantage du schéma, cependant, est qu’il peut détecter les deux types d’erreurs simultanément, il offre donc une protection plus robuste.

Cela a-t-il fonctionné ?

En général, le système a fonctionné. Dans ce qui est probablement la démonstration la plus claire, les chercheurs ont commencé le système de correction d’erreur linéaire avec une chaîne de cinq qubits, en ajoutant progressivement jusqu’à ce que la chaîne atteigne 21 qubits. Au fur et à mesure que la chaîne gagnait de plus en plus de qubits, elle est devenue progressivement plus robuste, le taux d’erreur diminuant d’un facteur 100 entre la chaîne de cinq et la chaîne de 21. Des erreurs se sont toutefois produites, donc la correction d’erreur n’est pas sans faille . Les performances sont restées stables jusqu’à 50 séries de contrôles d’erreurs.

Pour la deuxième configuration de correction d’erreurs, des erreurs se sont également produites, mais la plupart ont été détectées, et la nature précise des erreurs était généralement possible de déduire. Mais comme la configuration nécessite une géométrie plus précise pour fonctionner, l’équipe ne l’a pas étendue au-delà d’un nombre limité de qubits.

Les défaillances du système de correction d’erreurs se sont produites en partie parce qu’on demande au système de faire tellement. Pour le système linéaire, les chercheurs ont déterminé que 11% des contrôles ont fini par détecter une erreur, un nombre substantiel. C’est clairement une fonction de l’aspect « bruyant » de nos processeurs NISQ actuels, mais cela signifie également que la correction d’erreur doit être incroyablement efficace si elle est censée détecter chaque erreur. Et puisque le système fonctionne avec le même matériel, il est également soumis au même potentiel d’erreurs que les qubits de données.

Un autre problème que les chercheurs ont vu est un produit de la nature en chaîne du premier système. Étant donné que la chaîne parcourt le processeur, les qubits éloignés les uns des autres dans la chaîne peuvent se retrouver physiquement adjacents les uns aux autres. Cette proximité physique permet aux qubits de s’influencer, créant des erreurs corrélées dans les mesures.

Enfin, l’ensemble du système a parfois connu des performances extrêmement médiocres. Les chercheurs attribuent des problèmes de performances aux impacts des rayons cosmiques ou des sources de rayonnement locales frappant la puce. Bien que les problèmes ne soient pas répandus, ils se produisent suffisamment pour être un problème et s’intensifieront à mesure que le nombre de qubits continue d’augmenter, simplement parce que les processeurs présenteront une cible en constante augmentation.

Praticité

Finalement, nous n’en sommes pas encore là. Pour le deuxième schéma, où la détection d’erreurs provoquait le rejet du calcul, l’équipe de recherche a constaté que le système rejetait plus d’un quart des opérations. « Nous constatons que la performance globale de Sycomore [processors] doit être amélioré pour observer la suppression des erreurs dans [this] code », concèdent les chercheurs.

Même avec une chaîne longue de 21 qubits, le taux d’erreur a fini par être d’environ une opération sur 100 000. C’est certainement suffisant pour s’attendre à ce qu’un calcul puisse se poursuivre, les erreurs étant détectées et corrigées. Mais rappelez-vous : tous ces 21 qubits ont été utilisés pour encoder un seul qubit logique. Même le plus gros des processeurs actuels ne pouvait contenir que deux qubits avec ces systèmes.

Aucune de ces informations ne sera une surprise pour quiconque est impliqué dans le monde de l’informatique quantique, où il est généralement admis que nous aurons besoin d’environ un million de qubits avant de pouvoir corriger suffisamment de qubits pour effectuer des calculs utiles. Cela ne veut pas dire que les processeurs NISQ ne seront pas utiles avant cette date. S’il existe un calcul important qui nécessiterait un milliard d’années de temps de calcul intensif, l’exécuter plusieurs milliers de fois sur un processeur quantique est toujours raisonnable s’il produit un résultat sans erreur. Mais la vraie correction d’erreur devra clairement attendre.

Nature, 2021. DOI : 10.1038/s41586-021-03588-y (À propos des DOI).