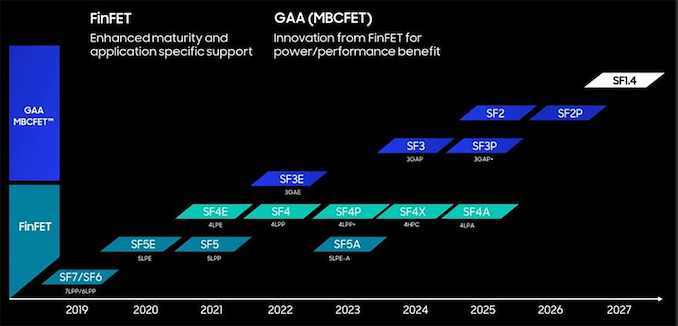

Samsung s’apprête à commencer à fabriquer des puces en utilisant ses 2sd Technologie de fabrication de classe 3 nm (SF3) de génération ainsi qu’une version aux performances améliorées de son processus de fabrication de classe 4 nm (SF4X) au second semestre de l’année prochaine, a déclaré la société à ses investisseurs cette semaine. Les deux pôles de production devraient améliorer considérablement la position concurrentielle de l’entreprise, car ils lui permettront de construire de nouveaux types de produits.

« Nous renforcerons notre compétitivité technologique grâce au 2H [2023] production en série du procédé 3 nm de 2ème génération ainsi que du 4ème processus de génération 4 nm pour le HPC », indique un communiqué de la société. « Le marché devrait évoluer vers la croissance grâce à un rebond de la demande mobile et à une croissance continue de la demande HPC. »

La prochaine technologie de processus SF3 de Samsung constitue une mise à niveau majeure de son nœud de production SF3E existant, qui, sur la base des connaissances disponibles, n’est utilisé que pour fabriquer de petites puces destinées à l’extraction de crypto-monnaie. Samsung affirme que le SF3 offrira une plus grande polyvalence de conception en permettant différentes largeurs de canaux de nanofeuilles de transistors à grille globale (GAA) au sein du même type de cellule.

Bien que Samsung ne fasse pas de comparaison directe entre le SF3 et le SF3E, il indique que le SF3 offre des améliorations majeures par rapport au SF4 (4LPP, classe 4 nm, faible consommation plus), qui incluent une augmentation de 22 % des performances à puissance et complexité équivalentes, ou alternativement, une réduction de 34 % de la consommation d’énergie à fréquence et nombre de transistors identiques, ainsi qu’une réduction de 21 % de la zone logique. De manière générale, on s’attend à ce que le SF3 soit une meilleure option que le SF3E pour les conceptions complexes, même s’il entrera en production en grand volume au cours du second semestre 2024.

Entre-temps, les nœuds de génération de classe 4 nm de Samsung Foundry continuent d’évoluer. La société se prépare à lancer sa technologie de processus SF4X (4HPC, calcul haute performance de classe 4 nm), conçue pour les applications hautes performances telles que les processeurs et les GPU utilisés dans les centres de données. Celui-ci sera le premier nœud de processus de SF ces dernières années spécialement conçu pour les applications de calcul haute performance (HPC).

La technologie de processus SF4X de Samsung promet d’offrir une amélioration de 10 % des performances ainsi qu’une réduction de 23 % de la consommation d’énergie. Bien que Samsung n’ait pas divulgué la base de référence pour cette comparaison, elle fait probablement référence à son processus standard SF4 (4LPP). Cette amélioration est obtenue grâce à une refonte des régions de source et de drain du transistor, suite à une réévaluation de leurs performances dans des conditions de contraintes potentiellement élevées, à l’application d’une co-optimisation avancée de la technologie de conception au niveau du transistor (T-DTCO) et à la mise en œuvre d’une nouvelle architecture middle-of-line (MOL).

Avec une architecture MOL raffinée, SF4X devrait atteindre une tension de fonctionnement minimale (Vmin) validée sur silicium pour les processeurs à 60 mV, réduire la variabilité du courant hors état (IDDQ) de 10 %, garantir un fonctionnement stable à haute tension (Vdd) au-dessus 1 V sans compromettre les performances et améliore la marge de processus pour la SRAM.

->Google Actualités